### **External CAN FD Controller with Integrated Transceiver**

#### **General Features**

- External CAN FD Controller with Integrated CAN FD Transceiver and Serial Peripheral Interface (SPI)

- Arbitration Bit Rate Up to 1 Mbps

- Data Bit Rate up to 5 Mbps

- CAN FD Controller Modes

- Mixed CAN 2.0B and CAN FD Mode

- CAN 2.0B Mode

- Fully ISO 11898-1:2015, ISO 11898-2: 2016 and SAE J2962-2 Compliant

- · Temperature Ranges:

- Extended (E): -40°C to +125°C

- High (H): -40°C to +150°C

- ISO 26262 Functional Safety Ready

- Low Electromagnetic Emission (EME) and High Electromagnetic Immunity (EMI)

- · AEC-Q100 and AEC-Q006 Qualified

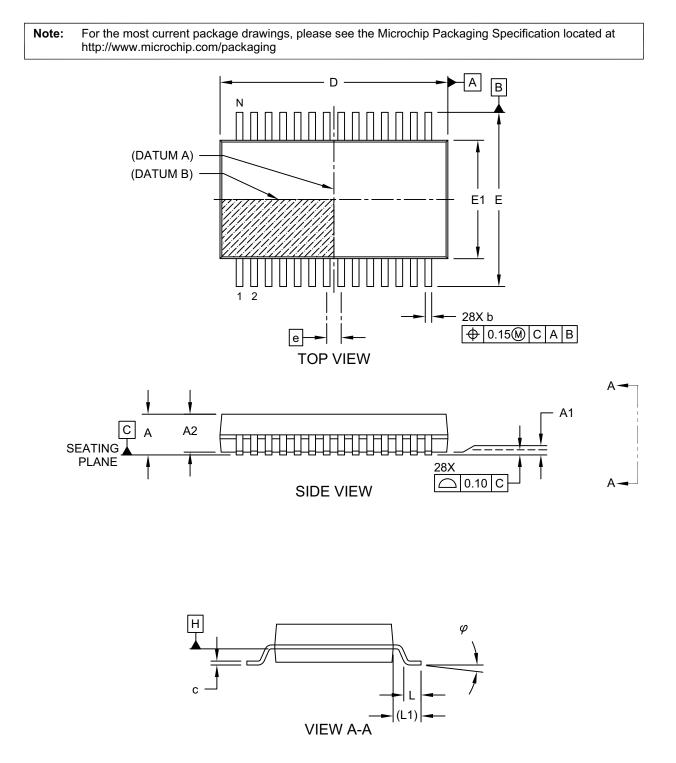

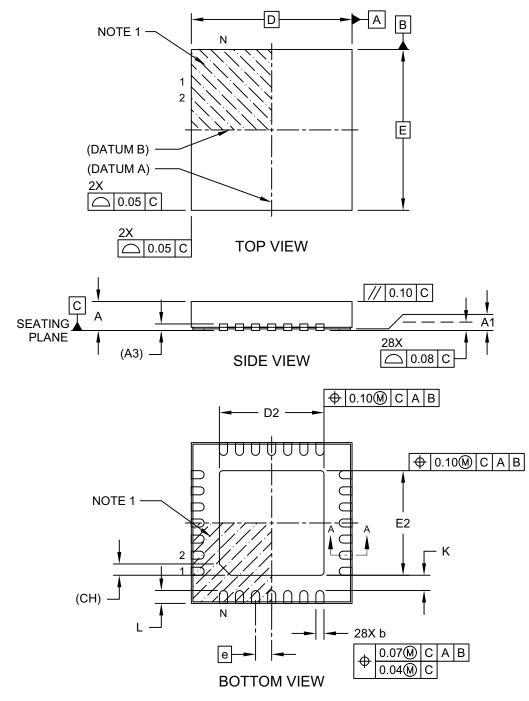

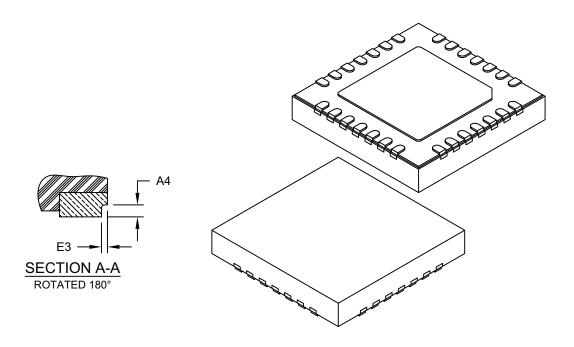

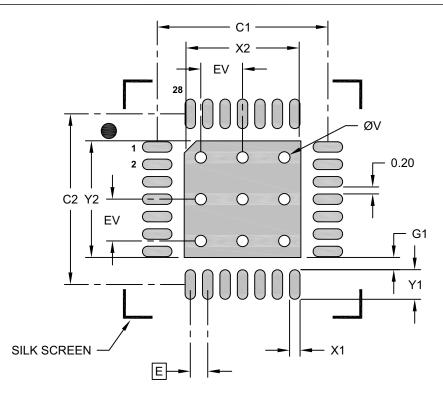

- Package: SSOP28 (Moisture Sensitivity Level 2), VQFN28 with Wettable Flanks (Moisture Sensitivity Level 1)

#### **CAN FD Controller Features**

#### Message FIFOs

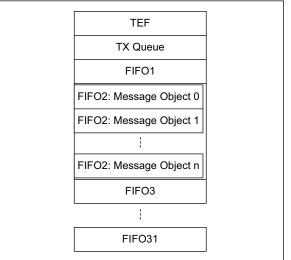

- 31 FIFOs, Configurable as Transmit or Receive FIFOs

- One Transmit Queue (TXQ)

- Transmit Event FIFO (TEF) with 32-bit Time Stamp

#### Message Transmission

- Message Transmission Prioritization:

- Based on Priority Bit Field

- Message with Lowest ID gets Transmitted First Using the Transmit Queue (TXQ)

- Programmable Automatic Retransmission Attempts: Unlimited, 3 Attempts or Disabled

#### Message Reception

- 32 Flexible Filter and Mask Objects

- · Each Object Can Be Configured to Filter Either:

- Standard ID + first 18 data bits, or

- Extended ID

- · 32-bit Time Stamp

#### **Special Features**

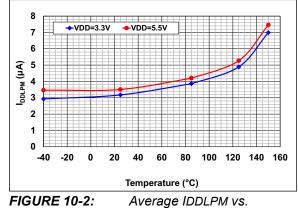

• VDD: 2.7V to 5.5V

- Active Current: Maximum 20 mA at 5.5 V, 40 MHz CAN clock

- Sleep Current: 15 μA, Typical

- Low Power Mode Current: Maximum 10  $\mu A$  from  $-40^\circ C$  to +150°C

- Message Objects are Located in RAM: 2 KB

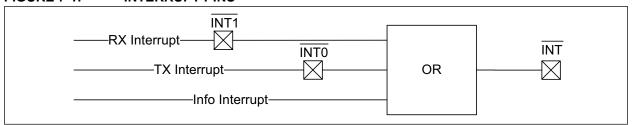

- · Up to 3 Configurable Interrupt Pins

- · Bus Health Diagnostics and Error Counters

- Transceiver Standby Control

- Start of Frame Pin for Indicating the Beginning of Messages on the Bus

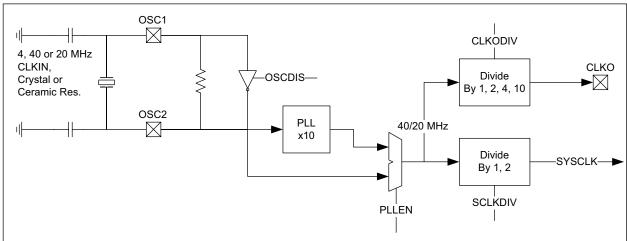

#### **Oscillator Options**

- 40, 20 or 4 MHz Crystal or Ceramic Resonator; External Clock Input

- Clock Output with Prescaler

#### SPI Interface

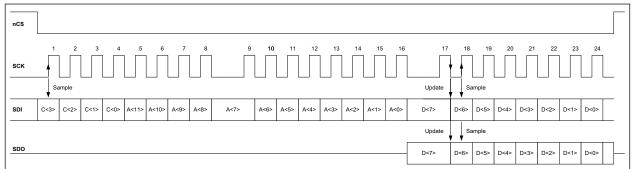

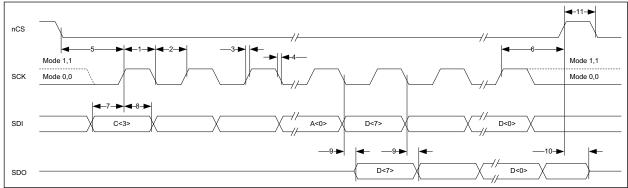

- Up to 20 MHz SPI Clock Speed

- Supports SPI Modes 0, 0 and 1, 1

- Registers and Bit Fields are Arranged in a Way to Enable Efficient Access through SPI

#### Safety Critical Systems

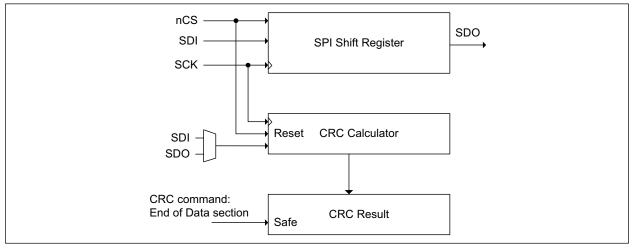

- SPI Commands with CRC to Detect Noise on SPI Interface

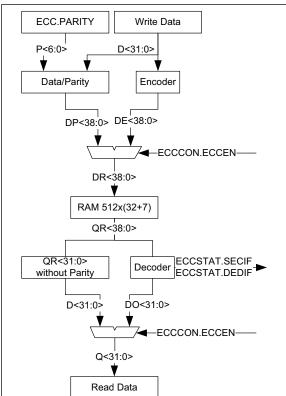

- · Error Correction Code (ECC) Protected RAM

#### **Additional Features**

- GPIO Pins: INT0 and INT1 Can Be Configured as General Purpose I/O

- Open Drain Outputs: TXCAN, INT, INTO, and INT1 Pins Can Be Configured as Push/Pull or Open Drain Outputs

#### **CAN FD Transceiver Features**

- Differential Receiver with Wide Common Mode Range

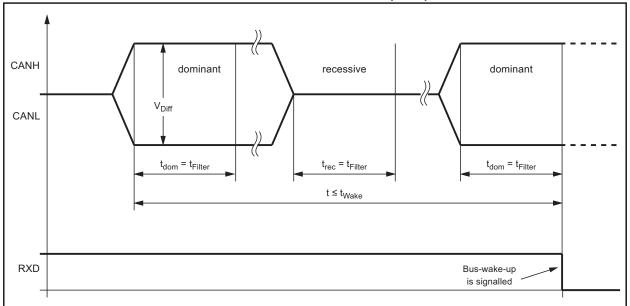

- Remote Wake-Up Capability via CAN Bus -Wake-Up on Pattern (WUP), as Specified in ISO 11898-2: 2016, 3.8 µs Activity Filter Time

- Functional Behavior Predictable under All Supply Conditions

- Transceiver Disengages from the Bus When Not Powered Up

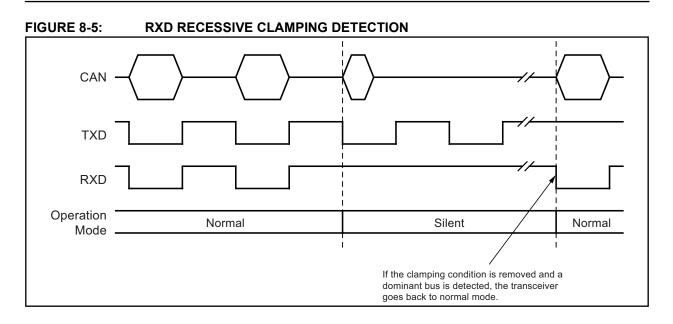

- RXD Recessive Clamping Detection

- High Electrostatic Discharge (ESD) Handling Capability on the Bus Pins

- · Bus Pins Protected Against Transients in

Automotive Environments

- Transmit Data (TXD) Dominant Time-Out Function

- Undervoltage Detection on VCC and VIO Pins

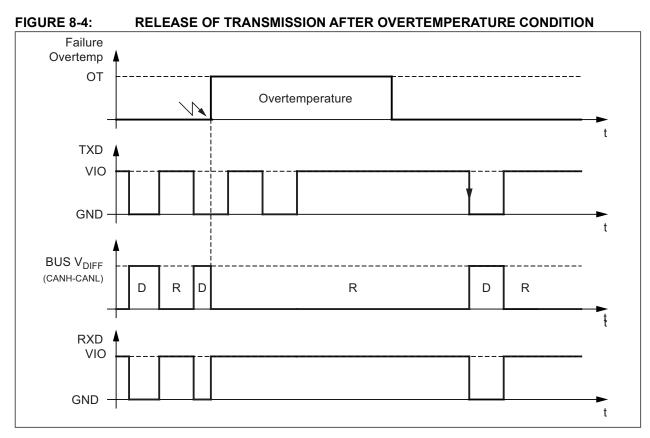

- CANH/CANL Short-Circuit and Overtemperature

Protected

#### Package Types

- + Low Max Standby Current of 12  $\mu\text{A}$

- Fulfills the OEM "Hardware Requirements for LIN, CAN and FlexRay Interfaces in Automotive Applications, Rev. 1.3"

#### 1.0 DEVICE OVERVIEW

The MCP251863 device is a cost-effective and small-footprint CAN FD controller (MCP2518FD) with an integrated Transceiver (ATA6563) that can be easily added to a microcontroller with an available SPI interface. A CAN FD channel can be easily added to a microcontroller that is either lacking a CAN FD peripheral or does not have enough CAN FD channels.

MCP251863 supports both CAN frames in the Classical format (CAN2.0B) and CAN Flexible Data Rate (CAN FD) format, as specified in ISO 11898-1:2015.

The integrated transceiver is a high-speed CAN FD Transceiver compliant with ISO 11898-2:2016 and SAE J2962-2 CAN standards. It provides a very low current consumption in Standby mode and wake-up capability via the CAN bus.

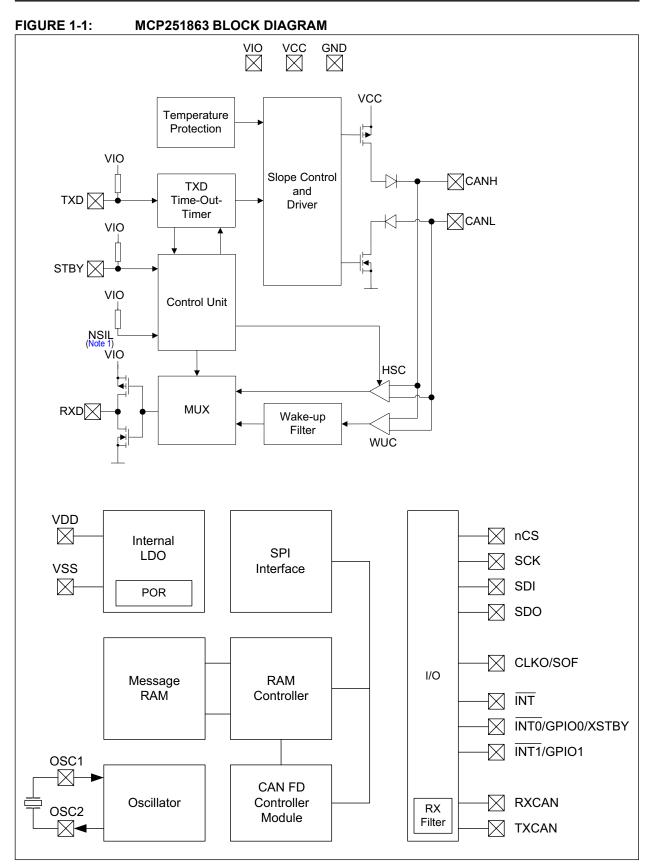

#### 1.1 Block Diagram

Figure 1-1 shows the block diagram of the MCP251863 device. MCP251863 contains the following main blocks:

- The CAN FD Controller module implements the CAN FD protocol, and contains the FIFOs and Filters.

- The SPI interface is used to control the device by accessing Special Function Registers (SFR) and RAM.

- The RAM controller arbitrates the RAM accesses between the SPI and CAN FD Controller module.

- The Message RAM is used to store the data of the Message Objects.

- The oscillator generates the CAN clock.

- The Internal LDO and POR circuit.

- The I/O control.

- The CAN FD Transceiver

- Note 1: This data sheet summarizes the features of the MCP251863 device. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual" (FRM).

Note 1: NSIL is not an externally available signal on this device and instead is pulled to VIO.

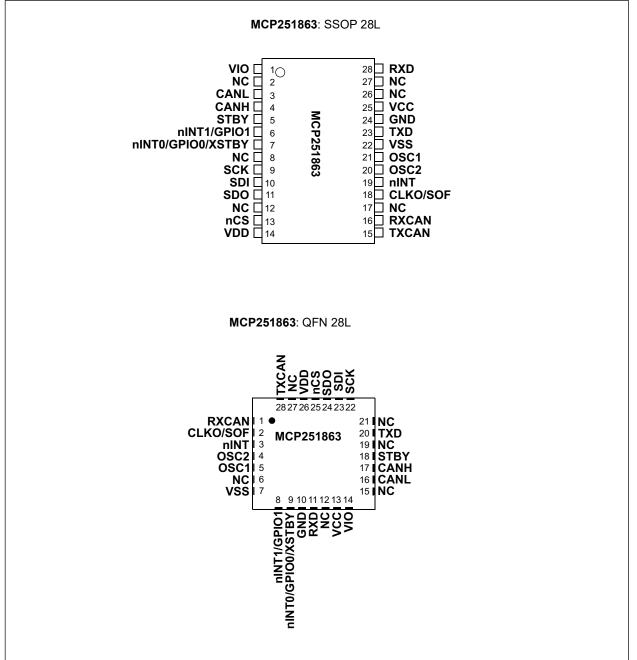

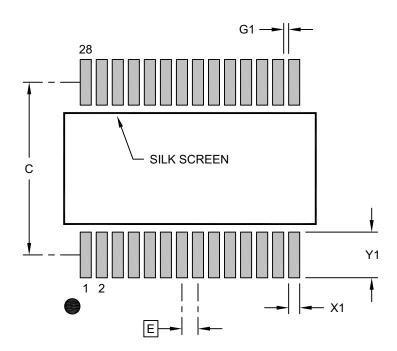

#### 1.2 Pinout Description

Table 1-1 describes the functions of the pins.

| Pin Name              | SSOP | VQFN | Pin Type | Description                                   |

|-----------------------|------|------|----------|-----------------------------------------------|

| TXCAN                 | 15   | 28   | 0        | Transmit output of the CAN FD Controller      |

| RXCAN                 | 16   | 1    | I        | Receive input of the CAN FD Controller        |

| CLKO/SOF              | 18   | 2    | 0        | Clock output/Test output                      |

| nINT                  | 19   | 3    | 0        | Interrupt output                              |

| OSC2                  | 20   | 4    | 0        | External oscillator output                    |

| OSC1                  | 21   | 5    | I        | External oscillator input                     |

| VSS                   | 22   | 7    | Power    | Ground                                        |

| nINT1/GPIO1           | 6    | 8    | I/O      | Interrupt output/GPIO                         |

| nINT0/GPIO0/<br>XSTBY | 7    | 9    | I/O      | Interrupt output/GPIO/<br>Transceiver Standby |

| SCK                   | 9    | 22   | I        | SPI clock input                               |

| SDI                   | 10   | 23   | I        | SPI data input                                |

| SDO                   | 11   | 24   | 0        | SPI data output                               |

| nCS                   | 13   | 25   | I        | SPI chip select input                         |

| VDD                   | 14   | 26   | Power    | Controller - Positive Supply                  |

| TXD                   | 23   | 20   | I        | Transmit Data Input                           |

| GND                   | 24   | 10   | Power    | Ground                                        |

| VCC                   | 25   | 13   | Power    | Transceiver - Positive Supply                 |

| RXD                   | 28   | 11   | 0        | Receive Data Output                           |

| VIO                   | 1    | 14   | Power    | Transceiver - Digital I/O Supply              |

| CANL                  | 3    | 16   | I/O      | CAN Low-Level Voltage                         |

| CANH                  | 4    | 17   | I/O      | CAN High-Level Voltage                        |

| STBY                  | 5    | 18   | I        | Standby Mode                                  |

| NC                    | 2    | 29   | NC       | No Connect                                    |

| NC                    | 8    | 6    | NC       | No Connect                                    |

| NC                    | 12   | 12   | NC       | No Connect                                    |

| NC                    | 17   | 15   | NC       | No Connect                                    |

| NC                    | 26   | 19   | NC       | No Connect                                    |

| NC                    | 27   | 21   | NC       | No Connect                                    |

#### TABLE 1-1: MCP251863 STANDARD PINOUT VERSION

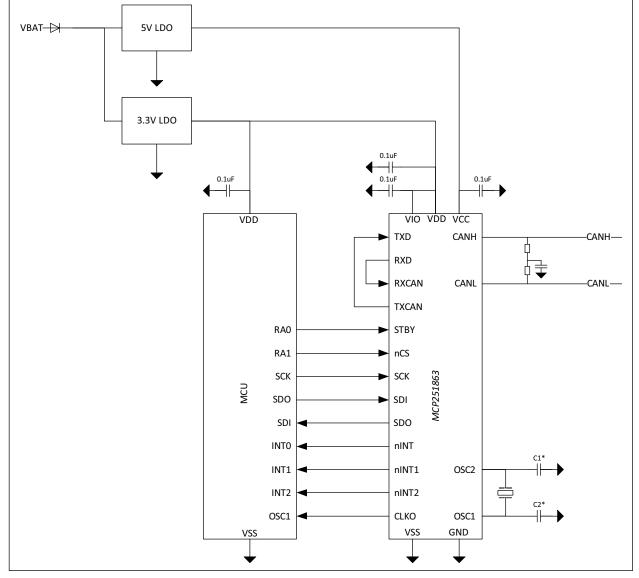

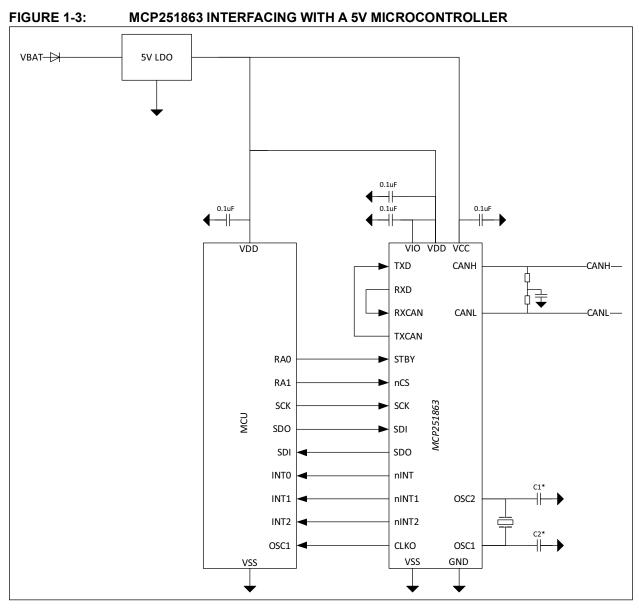

#### **1.3** Typical Application

Figure 1-2 shows an example of a typical application of the MCP251863 device. In this example, the microcontroller operates at 3.3V.

The MCP251863 device interfaces directly with microcontrollers operating at 2.7V to 5.5V. There are no external level shifters required when connecting VDD and VIO of the MCP251863 and the microcontroller.

The Vcc of the CAN FD transceiver is connected to 5V.

The SPI interface is used to configure and control the CAN FD controller.

The MCP251863 device signals interrupts to the microcontroller by using INT, INTO and INT1. Interrupts need to be cleared by the microcontroller through SPI.

The CLKO pin provides the clock to the microcontroller.

Note: Example capacitor values are listed in the FRM.

Note: Example capacitor values are listed in the FRM.

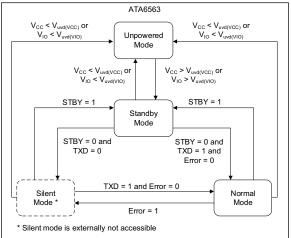

### 2.0 OPERATING MODES

#### 2.1 Operating Modes of the CAN FD Controller

The CAN FD Controller module has multiple modes:

- Configuration

- Normal CAN FD

- Normal CAN 2.0

- Sleep (normal Sleep mode and Low Power Mode)

- · Listen Only

- Restricted Operation

- Internal and External Loop back modes

The operational mode is selected via the REQOP[2:0] bits in the CiCON register (see Register 4-7: "CiCON – CAN Control Register")

When changing modes, the mode will not actually change until all pending message transmissions are completed. The requested mode must be verified by reading the OPMOD[2:0] bits in the CiCON register.

A detailed description of the Operating Modes can be found in the FRM.

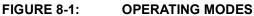

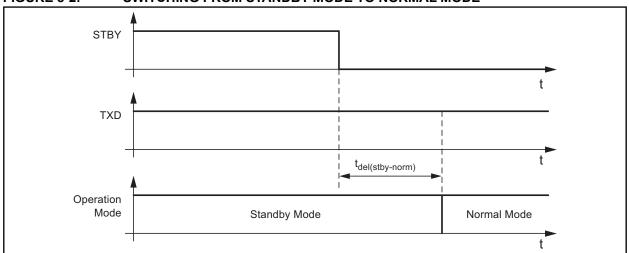

#### 2.2 CAN FD Transceiver Modes of Operation

The CAN FD Transceiver supports two modes of operation Standby and Normal mode. The mode is selected via the Standby pin. A detailed description can be found in section **Section 8.1, Operating Modes of the Transceiver**.

#### 2.3 Normal Mode

Normal mode is the standard operating mode of the MCP251863. In this mode, the device actively monitors all bus messages and generates Acknowledge bits, error frames, etc. This is also the only mode in which the MCP251863 transmits frames over the CAN bus.

The CAN FD Controller must be in Normal CAN FD or in Normal CAN 2.0 mode. The Transceiver must be in normal mode.

#### 2.4 Sleep/Standby Mode

The CAN FD Controller has two internal Sleep modes that are used to minimize the current consumption of the device. The SPI interface remains active for reading even when the MCP251863 is in Sleep mode, allowing access to all registers.

Sleep mode is selected via the REQOPx bits in the CiCON register. The OPMODx bits in the CiCON register indicate the operation mode. The bit OSCDIS in register OSC should be read after sending the

SLEEP command to the MCP251863. The MCP251863 is active and has not yet entered Sleep mode until the OSCDIS bit indicates that Sleep mode has been entered.

When in Sleep mode, the MCP251863 stops its internal oscillator. The MCP251863 will wake-up when bus activity occurs or when the microcontroller clears OSCDIS via the SPI interface. The WAKIF bit in the CiINT register will "generate" a wake-up event (the WAKIE bit in the CiINT register must also be set in order for the wake-up interrupt to occur).

The CAN FD transceiver must be in Standby mode in order to take advantage of the low standby current of the transceiver. After a wake-up, the microcontroller must put the transceiver back into Normal mode using the Standby pin.

The CAN FD Controller also supports an LP mode. For a detailed description of entering and exiting LPM mode refer to the FRM.

#### 3.0 CAN FD CONTROLLER MODULE

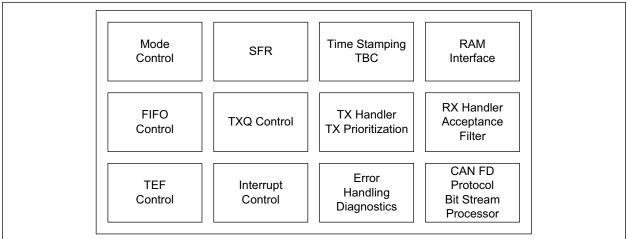

Figure 3-1 shows the main blocks of the CAN FD Controller module:

- The CAN FD Bit Stream Processor (BSP) implements the Medium Access Control of the CAN FD protocol described in ISO 11898-1:2015. It serializes and de-serializes the bit stream, encodes and decodes the CAN FD frames, manages the medium access, acknowledges frames and detects and signals errors.

- The TX Handler prioritizes the messages that are requested for transmission by the Transmit FIFOs. It uses the RAM Interface to fetch the transmit data from RAM and provides it to the BSP for transmission.

- The BSP provides received messages to the RX Handler. The RX Handler uses the Acceptance Filter to filter out messages that shall be stored into Receive FIFOs. It uses the RAM Interface to store received data into RAM.

- Each FIFO can be configured either as a Transmit or Receive FIFO. The FIFO Control keeps track of the FIFO Head and Tail, and calculates the User Address. For a TX FIFO, the User Address points to the address in RAM where the data for the next transmit message shall be stored. For a RX FIFO, the User Address points to the address in RAM where the data of the next receive message shall be read. The User notifies the FIFO that a message was written to or read from RAM by incrementing the Head/Tail of the FIFO.

- The Transmit Queue (TXQ) is a special transmit FIFO that transmits the messages based on the ID of the messages stored in the queue.

- The Transmit Event FIFO (TEF) stores the message IDs of the transmitted messages.

- A free-running Time Base Counter is used to time stamp received messages. Messages in the TEF can also be time stamped.

- The CAN FD Controller module generates interrupts when new messages are received or messages were transmitted successfully.

- The SFR are used to control and to read the status of the CAN FD Controller module.

Note 1: This data sheet summarizes the features of the CAN FD Controller module. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual".

#### FIGURE 3-1: CAN FD CONTROLLER MODULE BLOCK DIAGRAM

#### 4.0 MEMORY ORGANIZATION

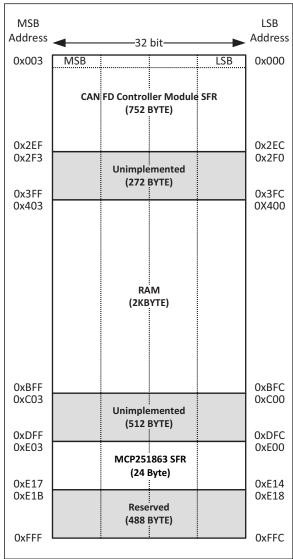

Figure 4-1 illustrates the main sections of the memory and its address ranges:

- MCP251863 Special Function Registers

- CAN FD Controller module SFR

- Message Memory (RAM)

The SFR are 32-bit wide. The LSB is located at the lower address, for example, the LSB of C1CON is located at address  $0 \times 000$ , while its MSB is located at address  $0 \times 003$ .

Table 4-1 lists the MCP251863 specific registers. The first column contains the address of the SFR.

Table 4-2 lists the registers of the CAN FD Controller module. The first column contains the address of the SFR.

#### FIGURE 4-1: MEMORY MAP

|                    |         |       |                   |                   |                   |                   |                   |                   |                  | 1                |

|--------------------|---------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Address            | Name    | )     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| E03                | OSC     | 31:24 |                   | —                 | _                 | —                 | —                 | —                 | —                | —                |

| E02                |         | 23:16 | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| E01                |         | 15:8  | _                 | —                 | —                 | SCLKRDY           | —                 | OSCRDY            | —                | PLLRDY           |

| E00 <sup>(1)</sup> |         | 7:0   |                   | CLKOE             | DIV[1:0]          | SCLKDIV           | LPMEN             | OSCDIS            | _                | PLLEN            |

|                    | IOCON   | 31:24 |                   | INTOD             | SOF               | TXCANOD           | —                 | _                 | PM1              | PM0              |

|                    |         | 23:16 | _                 | _                 | _                 | _                 | _                 | —                 | GPIO1            | GPIO0            |

|                    |         | 15:8  | _                 | _                 | _                 | _                 | _                 | _                 | LAT1             | LAT0             |

| E04                |         | 7:0   | _                 | XSTBYEN           | _                 | _                 | _                 | _                 | TRIS1            | TRIS0            |

|                    | CRC     | 31:24 | _                 | —                 | _                 | _                 | —                 | _                 | FERRIE           | CRCERRIE         |

|                    |         | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | FERRIF           | CRCERRIF         |

|                    |         | 15:8  |                   |                   |                   | CRC[              | [15:8]            |                   |                  |                  |

| E08                |         | 7:0   |                   | CRC[7:0]          |                   |                   |                   |                   |                  |                  |

|                    | ECCCON  | 31:24 |                   | —                 | _                 | —                 | —                 | —                 | —                | —                |

|                    |         | 23:16 | -                 | —                 | _                 | —                 | —                 | —                 | —                | —                |

|                    |         | 15:8  | _                 |                   |                   |                   | PARITY[6:0]       |                   |                  |                  |

| E0C                |         | 7:0   | _                 | _                 | _                 | _                 | _                 | DEDIE             | SECIE            | ECCEN            |

|                    | ECCSTAT | 31:24 |                   | —                 | —                 | _                 |                   | ERRADI            | DR[11:8]         |                  |

|                    |         | 23:16 |                   |                   |                   | ERRAD             | DR[7:0]           |                   |                  |                  |

|                    |         | 15:8  | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| E10                |         | 7:0   |                   | _                 | _                 | _                 | _                 | DEDIF             | SECIF            | _                |

|                    | DEVID   | 31:24 | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                    |         | 23:16 | _                 | _                 | —                 | —                 | —                 | —                 | _                | _                |

|                    |         | 15:8  | _                 | _                 | —                 | _                 | —                 | —                 | _                | _                |

| E14                |         | 7:0   |                   | ID[:              | 3:0]              |                   |                   | REV               | [3:0]            |                  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

2: The bit fields in the IOCON register must be written using single data byte SFR WRITE instructions.

| Addr.            | Name     |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------|----------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 03               | C1CON    | 31:24 |                   | TXBW              | /S[3:0]           |                   | ABAT              |                   | REQOP[2:0]       |                  |

| 02               |          | 23:16 |                   | OPMOD[2:0]        |                   | TXQEN             | STEF              | SERR2LOM          | ESIGM            | RTXAT            |

| 01               |          | 15:8  | —                 | _                 | _                 | BRSDIS            | BUSY              | WFT               | [1:0]            | WAKFIL           |

| 0 <sup>(1)</sup> |          | 7:0   | —                 | PXEDIS            | ISOCRCEN          |                   |                   | DNCNT[4:0]        |                  |                  |

|                  | C1NBTCFG | 31:24 |                   |                   |                   | BRF               | P[7:0]            |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   | TSEC              | G1[7:0]           |                   |                  |                  |

|                  |          | 15:8  | —                 |                   |                   |                   | TSEG2[6:0]        |                   |                  |                  |

| 04               |          | 7:0   | —                 |                   |                   |                   | SJW[6:0]          |                   |                  |                  |

|                  | C1DBTCFG | 31:24 |                   |                   |                   | BRF               | <b>P</b> [7:0]    |                   |                  |                  |

|                  |          | 23:16 | —                 | —                 | _                 |                   |                   | TSEG1[4:0]        |                  |                  |

|                  |          | 15:8  | —                 | —                 | _                 | —                 |                   | TSEG              | 62[3:0]          |                  |

| 08               |          | 7:0   | —                 | _                 | _                 | —                 |                   | SJW               | [3:0]            |                  |

|                  | C1TDC    | 31:24 | —                 | —                 |                   | —                 | —                 | —                 | EDGFLTEN         | SID11EN          |

|                  |          | 23:16 | —                 | —                 | _                 | —                 | —                 | -                 | TDCM             | DD[1:0]          |

|                  |          | 15:8  | —                 | —                 |                   |                   | TDC               | O[5:0]            |                  |                  |

| 0C               |          | 7:0   | —                 | _                 |                   |                   | TDC'              | V[5:0]            |                  |                  |

|                  | C1TBC    | 31:24 |                   |                   |                   | -                 | 31:24]            |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   | -                 | 23:16]            |                   |                  |                  |

|                  |          | 15:8  |                   |                   |                   | TBC               | [15:8]            |                   |                  |                  |

| 10               |          | 7:0   |                   |                   |                   | TBC               | [7:0]             |                   |                  |                  |

|                  | C1TSCON  | 31:24 | —                 |                   |                   | —                 | —                 | —                 | —                |                  |

|                  |          | 23:16 | —                 | —                 | _                 | —                 | —                 | TSRES             | TSEOF            | TBCEN            |

|                  |          | 15:8  | —                 | —                 | —                 | —                 | —                 | -                 | TBCPF            | RE[9:8]          |

| 14               |          | 7:0   |                   |                   |                   | TBCP              | RE[7:0]           |                   |                  |                  |

|                  | C1VEC    | 31:24 | —                 |                   |                   |                   | RXCODE[6:0]       |                   |                  |                  |

|                  |          | 23:16 | —                 |                   |                   |                   | TXCODE[6:0]       |                   |                  |                  |

|                  |          | 15:8  | —                 | _                 | —                 |                   |                   | FILHIT[4:0]       |                  |                  |

| 18               |          | 7:0   | —                 |                   |                   |                   | ICODE[6:0]        |                   |                  |                  |

|                  | C1INT    | 31:24 | IVMIE             | WAKIE             | CERRIE            | SERRIE            | RXOVIE            | TXATIE            | SPICRCIE         | ECCIE            |

|                  |          | 23:16 | —                 | —                 | _                 | TEFIE             | MODIE             | TBCIE             | RXIE             | TXIE             |

|                  |          | 15:8  | IVMIF             | WAKIF             | CERRIF            | SERRIF            | RXOVIF            | TXATIF            | SPICRCIF         | ECCIF            |

| 1C               |          | 7:0   | —                 | _                 | _                 | TEFIF             | MODIF             | TBCIF             | RXIF             | TXIF             |

|                  | C1RXIF   | 31:24 |                   |                   |                   |                   | 31:24]            |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   |                   | 23:16]            |                   |                  |                  |

|                  |          | 15:8  |                   |                   |                   | RFIF              | [15:8]            |                   |                  |                  |

| 20               |          | 7:0   |                   |                   |                   | RFIF[7:1]         |                   |                   |                  | —                |

|                  | C1TXIF   | 31:24 |                   |                   |                   |                   | 31:24]            |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   |                   | 23:16]            |                   |                  |                  |

|                  |          | 15:8  |                   |                   |                   |                   | [15:8]            |                   |                  |                  |

| 24 7:0 TFIF[7:0] |          |       |                   |                   |                   |                   |                   |                   |                  |                  |

|                  | C1RXOVIF | 31:24 |                   |                   |                   |                   | F[31:24]          |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   |                   | F[23:16]          |                   |                  |                  |

|                  |          | 15:8  |                   |                   |                   |                   | IF[15:8]          |                   |                  |                  |

| 28               |          | 7:0   |                   |                   |                   | RFOVIF[7:1]       |                   |                   |                  | —                |

|                  | C1TXATIF | 31:24 |                   |                   |                   |                   | [31:24]           |                   |                  |                  |

|                  |          | 23:16 |                   |                   |                   |                   | [23:16]           |                   |                  |                  |

|                  |          | 15:8  |                   |                   |                   |                   | F[15:8]           |                   |                  |                  |

| 2C               |          | 7:0   |                   |                   |                   | TFAT              | IF[7:0]           |                   |                  |                  |

#### TABLE 4-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Addr. | Name                    |             | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-------|-------------------------|-------------|-------------------|-------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|--|

|       | C1TXREQ                 | 31:24       |                   |                   |                   |                   | 2[31:24]           | -                 |                  |                  |  |  |

|       |                         | 23:16       |                   |                   |                   | TXREC             | 2[23:16]           |                   |                  |                  |  |  |

|       |                         | 15:8        |                   |                   |                   | TXRE              | Q[15:8]            |                   |                  |                  |  |  |

| 30    |                         | 7:0         |                   |                   |                   | TXRE              | Q[7:0]             |                   |                  |                  |  |  |

|       | C1TREC                  | 31:24       | —                 | —                 | -                 | —                 | —                  | —                 | —                | —                |  |  |

|       |                         | 23:16       | —                 | —                 | TXBO              | TXBP              | RXBP               | TXWARN            | RXWARN           | EWARN            |  |  |

|       |                         | 15:8        |                   |                   |                   | TEC               | [7:0]              |                   |                  |                  |  |  |

| 34    |                         | 7:0         |                   |                   |                   |                   | [7:0]              |                   |                  |                  |  |  |

|       | C1BDIAG0                | 31:24       |                   |                   |                   |                   | CNT[7:0]           |                   |                  |                  |  |  |

|       |                         | 23:16       |                   |                   |                   |                   | CNT[7:0]           |                   |                  |                  |  |  |

|       |                         | 15:8        |                   |                   |                   |                   | CNT[7:0]           |                   |                  |                  |  |  |

| 38    |                         | 7:0         |                   |                   |                   |                   | CNT[7:0]           |                   |                  |                  |  |  |

|       | C1BDIAG1                | 31:24       | DLCMM             | ESI               | DCRCERR           |                   | DFORMERR           | —                 | DBIT1ERR         | DBIT0ERR         |  |  |

|       |                         | 23:16       | TXBOERR           | —                 | NCRCERR           | NSTUFERR          | NFORMERR           | NACKERR           | NBIT1ERR         | NBIT0ERR         |  |  |

|       |                         | 15:8        |                   |                   |                   |                   | CNT[15:8]          |                   |                  |                  |  |  |

| 3C    |                         | 7:0         |                   |                   |                   | EFMSG             | CNT[7:0]           |                   |                  |                  |  |  |

|       | C1TEFCON                | 31:24       | —                 | —                 | -                 |                   | 1                  | FSIZE[4:0]        |                  |                  |  |  |

|       |                         | 23:16       | —                 | _                 | -                 | —                 | _                  | —                 | _                | —                |  |  |

|       |                         | 15:8        | _                 | _                 | -                 | _                 | _                  | FRESET            | —                | UINC             |  |  |

| 40    |                         | 7:0         | —                 | —                 | TEFTSEN           | —                 | TEFOVIE            | TEFFIE            | TEFHIE           | TEFNEIE          |  |  |

|       | C1TEFSTA                | 31:24       | _                 | _                 | _                 | _                 | _                  | _                 | _                | _                |  |  |

|       |                         | 23:16       | _                 |                   | _                 | _                 | _                  | _                 | _                | _                |  |  |

|       |                         | 15:8        | _                 |                   | _                 | _                 | -                  | -                 | -                | -                |  |  |

| 44    |                         | 7:0         | TEFUA[31:24]      |                   |                   |                   |                    |                   |                  |                  |  |  |

|       | C1TEFUA                 | 31:24       |                   |                   |                   |                   |                    |                   |                  |                  |  |  |

|       |                         | 23:16       |                   |                   |                   |                   | A[23:16]           |                   |                  |                  |  |  |

| 40    |                         | 15:8<br>7:0 |                   |                   |                   |                   | A[15:8]<br>IA[7:0] |                   |                  |                  |  |  |

| 48    | Reserved <sup>(2)</sup> | 31:24       |                   |                   |                   |                   | ed[31:24]          |                   |                  |                  |  |  |

|       | Reserved                | 23:16       |                   |                   |                   |                   | ed[23:16]          |                   |                  |                  |  |  |

|       |                         | 15:8        |                   |                   |                   |                   | ed[15:8]           |                   |                  |                  |  |  |

| 4C    |                         | 7:0         |                   |                   |                   |                   | /ed[7:0]           |                   |                  |                  |  |  |

| 40    | C1TXQCON                | 31:24       |                   | PLSIZE[2:0]       |                   |                   | red[r.0]           | FSIZE[4:0]        |                  |                  |  |  |

|       | OTIXQUUN                | 23:16       | _                 | TXA               | [1:0]             |                   |                    | TXPRI[4:0]        |                  |                  |  |  |

|       |                         | 15:8        |                   | _                 |                   | _                 | _                  | FRESET            | TXREQ            | UINC             |  |  |

| 50    |                         | 7:0         | TXEN              |                   | _                 | TXATIE            | _                  | TXQEIE            | _                | TXQNIE           |  |  |

|       | C1TXQSTA                | 31:24       | _                 | _                 | _                 | _                 | _                  | _                 | _                | _                |  |  |

|       |                         | 23:16       | _                 |                   | _                 | _                 | _                  |                   | _                | _                |  |  |

|       |                         | 15:8        | _                 | _                 | _                 |                   |                    | TXQCI[4:0]        |                  |                  |  |  |

| 54    |                         | 7:0         | TXABT             | TXLARB            | TXERR             | TXATIF            | —                  | TXQEIF            | _                | TXQNIF           |  |  |

|       | C1TXQUA                 | 31:24       |                   |                   |                   | TXQUA             | A[31:24]           |                   |                  |                  |  |  |

|       |                         | 23:16       |                   |                   |                   | TXQUA             | A[23:16]           |                   |                  |                  |  |  |

|       |                         | 15:8        |                   |                   |                   | TXQU              | A[15:8]            |                   |                  |                  |  |  |

| 58    |                         | 7:0         |                   |                   |                   | TXQL              | JA[7:0]            |                   |                  |                  |  |  |

TABLE 4-2:

CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

| Addr. | Name        |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------|-------------|-------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|       | C1FIFOCON1  | 31:24 |                   | PLSIZE[2:0]        |                   |                   |                   | FSIZE[4:0]        |                  |                  |

|       |             | 23:16 | —                 | TXAT               | [1:0]             |                   |                   | TXPRI[4:0]        |                  |                  |

|       |             | 15:8  | —                 | —                  | —                 | —                 | —                 | FRESET            | TXREQ            | UINC             |

| 5C    |             | 7:0   | TXEN              | RTREN              | RXTSEN            | TXATIE            | RXOVIE            | TFERFFIE          | TFHRFHIE         | TFNRFNI          |

|       | C1FIFOSTA1  | 31:24 | —                 | —                  | —                 | _                 | —                 | —                 | —                | —                |

|       |             | 23:16 | —                 | —                  | —                 | —                 | —                 | —                 | —                | —                |

|       |             | 15:8  | —                 | —                  | _                 |                   |                   | FIFOCI[4:0]       |                  |                  |

| 60    |             | 7:0   | TXABT             | TXLARB             | TXERR             | TXATIF            | RXOVIF            | TFERFFIF          | TFHRFHIF         | TFNRFNI          |

|       | C1FIFOUA1   | 31:24 |                   |                    |                   | FIFOU             | 4[31:24]          |                   |                  |                  |

|       |             | 23:16 |                   |                    |                   | FIFOU             | 4[23:16]          |                   |                  |                  |

|       |             | 15:8  |                   |                    |                   | FIFOU             | A[15:8]           |                   |                  |                  |

| 64    |             | 7:0   |                   |                    |                   | FIFOL             | JA[7:0]           |                   |                  |                  |

| 68    | C1FIFOCON2  | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| 6C    | C1FIFOSTA2  | 31:0  |                   |                    |                   | same as C         |                   |                   |                  |                  |

| 70    | C1FIFOUA2   | 31:0  |                   | same as C1FIFOUA1  |                   |                   |                   |                   |                  |                  |

| 74    | C1FIFOCON3  | 31:0  |                   | same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 78    | C1FIFOSTA3  | 31:0  |                   | same as C1FIFOSTA1 |                   |                   |                   |                   |                  |                  |

| 7C    | C1FIFOUA3   | 31:0  |                   | same as C1FIFOUA1  |                   |                   |                   |                   |                  |                  |

| 80    | C1FIFOCON4  | 31:0  |                   | same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 84    | C1FIFOSTA4  | 31:0  |                   | same as C1FIFOSTA1 |                   |                   |                   |                   |                  |                  |

| 88    | C1FIFOUA4   | 31:0  |                   | same as C1FIFOUA1  |                   |                   |                   |                   |                  |                  |

| 8C    | C1FIFOCON5  | 31:0  |                   | same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 90    | C1FIFOSTA5  | 31:0  |                   | same as C1FIFOSTA1 |                   |                   |                   |                   |                  |                  |

| 94    | C1FIFOUA5   | 31:0  |                   | same as C1FIFOUA1  |                   |                   |                   |                   |                  |                  |

| 98    | C1FIFOCON6  | 31:0  |                   | same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 9C    | C1FIFOSTA6  | 31:0  |                   | same as C1FIFOSTA1 |                   |                   |                   |                   |                  |                  |

| A0    | C1FIFOUA6   | 31:0  |                   | same as CTFIFOSTAT |                   |                   |                   |                   |                  |                  |

| A4    | C1FIFOCON7  | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| A8    | C1FIFOSTA7  | 31:0  |                   |                    |                   |                   | 1FIFOSTA1         |                   |                  |                  |

| AC    | C1FIFOUA7   | 31:0  |                   |                    |                   | same as C         |                   |                   |                  |                  |

| B0    | C1FIFOCON8  | 31:0  |                   |                    |                   | same as C1        |                   |                   |                  |                  |

| B4    | C1FIFOSTA8  | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| B8    | C1FIFOUA8   | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| BC    | C1FIFOCON9  | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| C0    | C1FIFOSTA9  | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| C4    | C1FIFOUA9   | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| C8    | C1FIFOCON10 | 31:0  |                   |                    |                   | same as C1        | 1FIFOCON1         |                   |                  |                  |

| CC    | C1FIFOSTA10 | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| D0    | C1FIFOUA10  | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| D4    | C1FIFOCON11 | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| D8    | C1FIFOSTA11 | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| DC    | C1FIFOUA11  | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| E0    | C1FIFOCON12 | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| E4    | C1FIFOSTA12 | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| E8    | C1FIFOUA12  | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| EC    | C1FIFOCON13 | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| F0    | C1FIFOSTA13 | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| F4    | C1FIFOUA13  | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| F8    | C1FIFOCON14 | 31:0  |                   |                    |                   | same as C1        | IFIFOCON1         |                   |                  |                  |

| FC    | C1FIFOSTA14 | 31:0  |                   |                    |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 100   | C1FIFOUA14  | 31:0  |                   |                    |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

#### TABLE 4-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

| Addr.      | Name        |      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------|-------------|------|-------------------|--------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 104        | C1FIFOCON15 | 31:0 |                   |                                      | 1                 | same as C         | IFIFOCON1         | 1                 |                  | <u></u>          |

| 108        | C1FIFOSTA15 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 10C        | C1FIFOUA15  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 110        | C1FIFOCON16 | 31:0 |                   |                                      |                   |                   | IFIFOCON1         |                   |                  |                  |

| 114        | C1FIFOSTA16 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 118        | C1FIFOUA16  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 11C        | C1FIFOCON17 | 31:0 |                   |                                      |                   |                   | IFIFOCON1         |                   |                  |                  |

| 120        | C1FIFOSTA17 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 124        | C1FIFOUA17  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 128        | C1FIFOCON18 | 31:0 |                   | same as C1FIFOCON1                   |                   |                   |                   |                   |                  |                  |

| 12C        | C1FIFOSTA18 | 31:0 |                   | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |

| 130        | C1FIFOUA18  | 31:0 |                   | same as C1FIFOUA1                    |                   |                   |                   |                   |                  |                  |

| 134        | C1FIFOCON19 | 31:0 |                   | same as C1FIFOCON1                   |                   |                   |                   |                   |                  |                  |

| 138        | C1FIFOSTA19 | 31:0 |                   | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |

| 13C        | C1FIFOUA19  | 31:0 |                   | same as CTFIFOUA1                    |                   |                   |                   |                   |                  |                  |

| 140        | C1FIFOCON20 | 31:0 |                   | same as C1FIFOUA1 same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 144        | C1FIFOSTA20 | 31:0 |                   |                                      |                   | -                 | 1FIFOSTA1         |                   |                  |                  |

| 148        | C1FIFOUA20  | 31:0 |                   |                                      |                   |                   | IFIFOUA1          |                   |                  |                  |

| 140<br>14C | C1FIFOCON21 | 31:0 |                   |                                      |                   |                   | IFIFOCON1         |                   |                  |                  |

| 140        | C1FIFOSTA21 | 31:0 |                   |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |

| 150        | C1FIFOUA21  | 31:0 |                   |                                      |                   |                   |                   |                   |                  |                  |

| 154        | C1FIFOCON22 | 31:0 |                   |                                      |                   |                   | IFIFOUA1          |                   |                  |                  |

|            |             |      |                   |                                      |                   | -                 |                   |                   |                  |                  |

| 15C        | C1FIFOSTA22 | 31:0 |                   | same as C1FIFOSTA1 same as C1FIFOUA1 |                   |                   |                   |                   |                  |                  |

| 160        | C1FIFOUA22  | 31:0 |                   | same as C1FIFOUA1 same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |

| 164        | C1FIFOCON23 | 31:0 |                   |                                      |                   |                   |                   |                   |                  |                  |

| 168        | C1FIFOSTA23 | 31:0 |                   | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |

| 16C        | C1FIFOUA23  | 31:0 |                   | same as C1FIFOUA1                    |                   |                   |                   |                   |                  |                  |

| 170        | C1FIFOCON24 | 31:0 |                   |                                      |                   |                   | IFIFOCON1         |                   |                  |                  |

| 174        | C1FIFOSTA24 | 31:0 |                   |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |

| 178        | C1FIFOUA24  | 31:0 |                   |                                      |                   |                   | IFIFOUA1          |                   |                  |                  |

| 17C        | C1FIFOCON25 | 31:0 |                   |                                      |                   |                   | IFIFOCON1         |                   |                  |                  |

| 180        | C1FIFOSTA25 | 31:0 |                   |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |

| 184        | C1FIFOUA25  | 31:0 |                   |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |

| 188        | C1FIFOCON26 | 31:0 |                   |                                      |                   | -                 | IFIFOCON1         |                   |                  |                  |

| 18C        | C1FIFOSTA26 | 31:0 |                   |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |

| 190        | C1FIFOUA26  | 31:0 |                   |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |

| 194        | C1FIFOCON27 | 31:0 |                   |                                      |                   | -                 | IFIFOCON1         |                   |                  |                  |

| 198        | C1FIFOSTA27 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 19C        | C1FIFOUA27  | 31:0 |                   |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |

| 1A0        | C1FIFOCON28 | 31:0 |                   |                                      |                   | same as C         | IFIFOCON1         |                   |                  |                  |

| 1A4        | C1FIFOSTA28 | 31:0 |                   | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |

| 1A8        | C1FIFOUA28  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 1AC        | C1FIFOCON29 | 31:0 |                   |                                      |                   | same as C         | IFIFOCON1         |                   |                  |                  |

| 1B0        | C1FIFOSTA29 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 1B4        | C1FIFOUA29  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 1B8        | C1FIFOCON30 | 31:0 |                   |                                      |                   | same as C         | IFIFOCON1         |                   |                  |                  |

| 1BC        | C1FIFOSTA30 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 1C0        | C1FIFOUA30  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

| 1C4        | C1FIFOCON31 | 31:0 |                   |                                      |                   | same as C         | 1FIFOCON1         |                   |                  |                  |

| 1C8        | C1FIFOSTA31 | 31:0 |                   |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |

| 1CC        | C1FIFOUA31  | 31:0 |                   |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Addr.      | Name                 |              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------|----------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|            | C1FLTCON0            | 31:24        | FLTEN3            |                   | —                 |                   |                   | F3BP[4:0]         |                  |                  |

|            |                      | 23:16        | FLTEN2            | —                 | -                 |                   |                   | F2BP[4:0]         |                  |                  |

|            |                      | 15:8         | FLTEN1            | _                 | -                 |                   |                   | F1BP[4:0]         |                  |                  |

| 1D0        |                      | 7:0          | FLTEN0            | _                 | _                 |                   |                   | F0BP[4:0]         |                  |                  |

|            | C1FLTCON1            | 31:24        | FLTEN7            | _                 | -                 |                   |                   | F7BP[4:0]         |                  |                  |

|            |                      | 23:16        | FLTEN6            | _                 | _                 |                   |                   | F6BP[4:0]         |                  |                  |

|            |                      | 15:8         | FLTEN5            | _                 | _                 |                   |                   | F5BP[4:0]         |                  |                  |

| 1D4        |                      | 7:0          | FLTEN4            | _                 | -                 |                   |                   | F4BP[4:0]         |                  |                  |

|            | C1FLTCON2            | 31:24        | FLTEN11           | _                 | -                 |                   |                   | F11BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN10           | _                 | _                 |                   |                   | F10BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN9            | _                 | _                 |                   |                   | F9BP[4:0]         |                  |                  |

| 1D8        |                      | 7:0          | FLTEN8            | _                 | _                 |                   |                   | F8BP[4:0]         |                  |                  |

|            | C1FLTCON3            | 31:24        | FLTEN15           | _                 | _                 |                   |                   | F15BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN14           | _                 | _                 |                   |                   | F14BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN13           | _                 | _                 |                   |                   | F13BP[4:0]        |                  |                  |

| 1DC        |                      | 7:0          | FLTEN12           | _                 | _                 |                   |                   | F12BP[4:0]        |                  |                  |

|            | C1FLTCON4            | 31:24        | FLTEN19           | _                 | _                 |                   |                   | F19BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN18           |                   | _                 |                   |                   | F18BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN17           |                   | _                 |                   |                   | F17BP[4:0]        |                  |                  |

| 1E0        |                      | 7:0          | FLTEN16           |                   | _                 |                   |                   | F16BP[4:0]        |                  |                  |

|            | C1FLTCON5            | 31:24        | FLTEN23           |                   | _                 |                   |                   | F23BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN22           |                   | _                 |                   |                   | F22BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN21           |                   |                   |                   |                   | F21BP[4:0]        |                  |                  |

| 1E4        |                      | 7:0          | FLTEN20           |                   |                   |                   |                   | F20BP[4:0]        |                  |                  |

|            | C1FLTCON6            | 31:24        | FLTEN27           |                   |                   |                   |                   | F27BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN26           |                   |                   |                   |                   | F26BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN25           |                   |                   |                   |                   | F25BP[4:0]        |                  |                  |

| 1E8        |                      | 7:0          | FLTEN24           |                   |                   |                   |                   | F24BP[4:0]        |                  |                  |

| 1L0        | C1FLTCON7            | 31:24        | FLTEN31           |                   | _                 |                   |                   | F31BP[4:0]        |                  |                  |

|            |                      | 23:16        | FLTEN30           |                   |                   |                   |                   | F30BP[4:0]        |                  |                  |

|            |                      | 15:8         | FLTEN29           |                   |                   |                   |                   | F29BP[4:0]        |                  |                  |

| 1EC        |                      | 7:0          | FLTEN28           |                   |                   |                   |                   | F28BP[4:0]        |                  |                  |

| IEC        | C1FLTOBJ0            | 31:24        |                   |                   |                   |                   |                   |                   |                  |                  |

|            | CIFLIOBJU            | 23:16        | —                 | EXIDE             | SID11             |                   | 12:5]             | EID[17:6]         |                  |                  |

|            |                      | 15:8         |                   |                   |                   | EID[              | 12.0]             |                   | 010[40.0]        |                  |

| 450        |                      |              |                   |                   | EID[4:0]          |                   | [7.0]             |                   | SID[10:8]        |                  |

| 1F0        |                      | 7:0          |                   |                   |                   | SID               | [7:0]             |                   |                  |                  |

|            | C1MASK0              | 31:24        | _                 | MIDE              | MSID11            |                   | 10.51             | MEID[17:6]        |                  |                  |

|            |                      | 23:16        |                   |                   |                   | MEID              | [12:5]            | 1                 | MOID[40:0]       |                  |

| 454        |                      | 15:8         |                   |                   | MEID[4:0]         | MOI               | 217.01            |                   | MSID[10:8]       |                  |

| 1F4        |                      | 7:0          |                   |                   |                   |                   | D[7:0]            |                   |                  |                  |

| 1F8        | C1FLTOBJ1            | 31:0         |                   |                   |                   |                   | 1FLTOBJ0          |                   |                  |                  |

| 1FC        | C1MASK1              | 31:0         |                   |                   |                   |                   | C1MASK0           |                   |                  |                  |

| 200        | C1FLTOBJ2            | 31:0<br>31:0 |                   |                   |                   |                   | 1FLTOBJ0          |                   |                  |                  |

| 204        | C1MASK2<br>C1FLTOBJ3 | 31:0         |                   |                   |                   |                   | C1MASK0           |                   |                  |                  |

| 208<br>20C | C1FLTOBJ3<br>C1MASK3 | 31:0<br>31:0 |                   |                   |                   |                   | C1MASK0           |                   |                  |                  |

| 200        | C1MASK3              | 31:0         |                   |                   |                   |                   | TFLTOBJ0          |                   |                  |                  |

| 210        | C1FL10BJ4            | 31:0         |                   |                   |                   |                   | C1MASK0           |                   |                  |                  |

| 214        | C1FLTOBJ5            | 31:0         |                   |                   |                   |                   | TFLTOBJ0          |                   |                  |                  |

| 210<br>21C | C1MASK5              | 31:0         |                   |                   |                   |                   | C1MASK0           |                   |                  |                  |

| - 10       |                      |              |                   | bit register re   |                   |                   |                   |                   |                  |                  |

#### TABLE 4-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| 224         C           228         C           220         C           230         C           234         C           238         C           238         C           238         C           230         C           234         C           238         C           230         C           238         C           240         C1           244         C           250         C1           254         C           255         C1           266         C1           267         C           268         C1           270         C1           274         C           270         C1           274         C           276         C           280         C1           284         C           288         C1           290         C1           294         C           292         C           294         C    | C1FLTOBJ6<br>C1MASK6<br>C1FLTOBJ7<br>C1MASK7<br>C1FLTOBJ8<br>C1FLTOBJ8<br>C1MASK8<br>C1FLTOBJ9<br>C1MASK9<br>C1FLTOBJ9<br>C1MASK10<br>C1MASK11<br>C1MASK11<br>C1MASK12<br>C1MASK12<br>C1MASK13<br>C1MASK13<br>C1MASK13<br>C1MASK13<br>C1MASK13 | 31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0 |   |                                      |                   | same as<br>same as C<br>same as C<br>same as C<br>same as C<br>same as C<br>same as C<br>same as C | C1MASK0                                                              |  |                   |   |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|-------------------|---|--|--|--|--|--|