# 16-Channel, 3-Level HV Ultrasound Transmitter with Built-in Transmit Beamformer

#### **Features**

- · 16-Channel with Active Return to True Zero

- Up to ±80V Output Voltage and ±1.6A Output Current

- Programmable Output Current: 0.3A, 0.5A, 1.0A and 1.6A

- -40 dB Second Harmonic at 5 MHz, ±70V, 5-Cycle

- Built-in T/R Switch, Damper and Protection Diodes

- · Built-in Linear Regulators for Floating Gate Driver

- Internal Low Jitter Phase-Locked Loop (PLL) Clock Multiplier for TX<sub>CH</sub> Clock

- 30 MHz to 80 MHz Input Clock Frequency in PLL Mode

- 30 MHz to 200 MHz Input Clock Frequency (in Non-PLL Mode) over Low-Voltage Differential Signaling (LVDS) Connection

- PLL Frequency Integer Multiplier x1, x2, x3, x4, x5, x6, x8

- Internal Clock Frequency (f<sub>C</sub>), up to 200 MHz to Allow a 5 ns Delay Resolution

- Ensured Synchronize Internal Transmit Clock Across Devices in the Same Phase

- PLL Circuit can be Bypassed and Shut Down to Reduce the Power Consumption

- Built-in Active Bleeder Circuit on V<sub>PP</sub> and V<sub>NN</sub> for Rapid Capacitor Discharging to Reduce the Time Required for Transmit Voltage Adjustment

- · Configurable 12-Bit Delay for Beamform per Channel

- Stores up to Four TX<sub>CH</sub> Patterns with the Optional Local t<sub>OFF</sub> Counter, Allowing the TX<sub>CH</sub> Apodization Use of the Pulse-Width Modulator (PWM)

- TX<sub>CH</sub> Patterns, up to 255 Pulses with Programmable Pulse Width and Frequency

- Programmable Continuous Wave (CW)

Frequency Divide Ratio, from 1 to 255 of the Input Clock Frequency

- Set-and-Go Feature in CW Mode Reduces the Digital Cross-Coupled Noise on PCB

- High-Speed LVDS SPI, Typical 200 MHz Operation Allows Fast Device Programming

- · SPI Group Broadcast Mode for Fast Data Writing

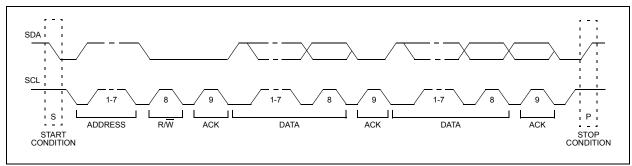

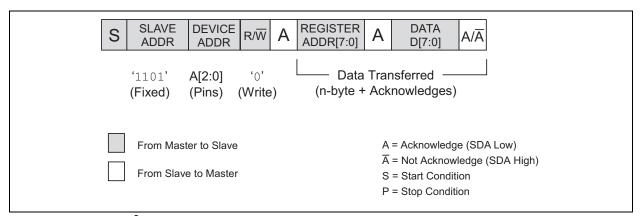

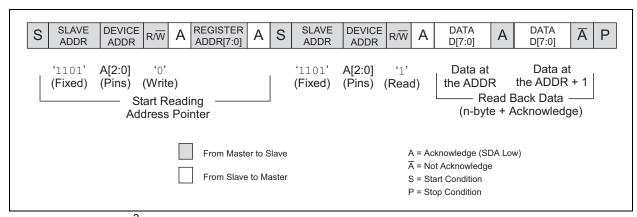

- Two-Wire I<sup>2</sup>C Interface for Control and Status Reading

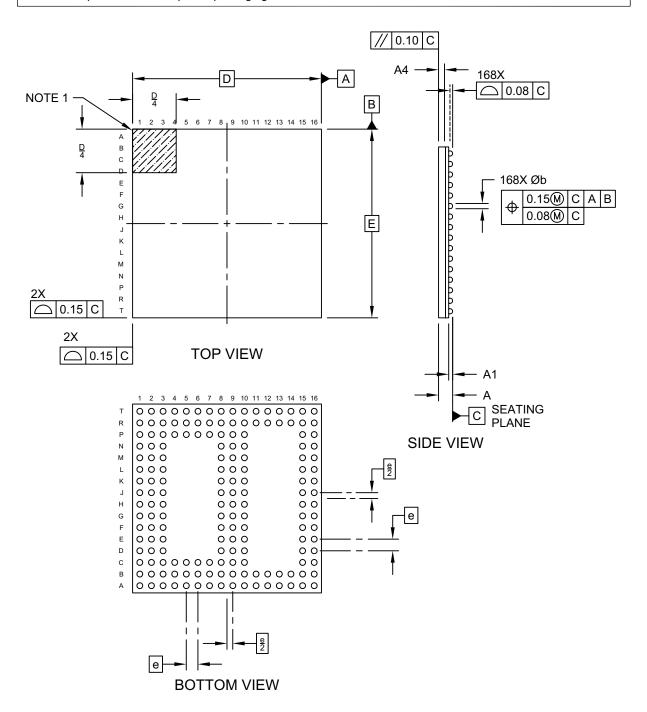

- 13 mm x 13 mm TFBGA Package with 0.8 mm Pitch

#### **Applications**

- Medical Portable Notebook Size and Trolley Size Ultrasound Imaging System

- · NDT Ultrasound Pulsers and Industrial Use

- · HV Pulse Pattern Generators

#### **General Description**

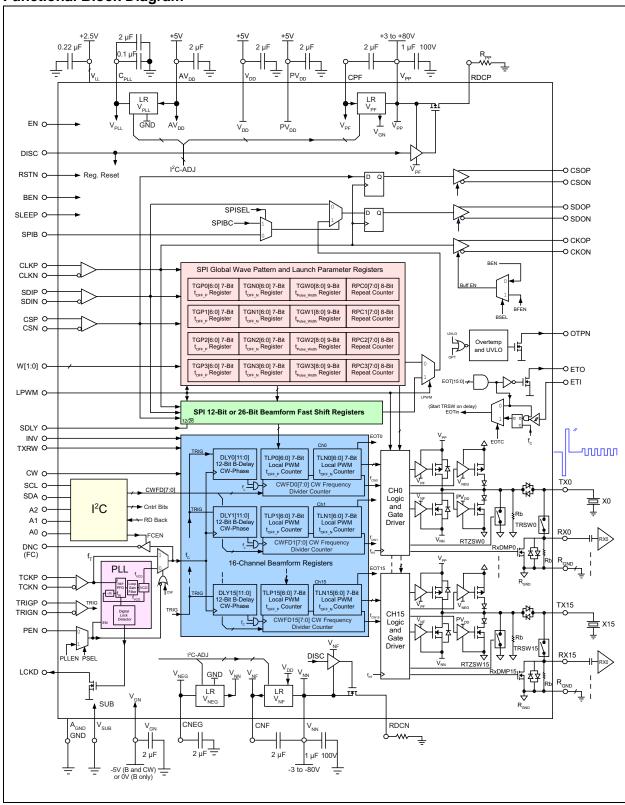

The HV7358 is a 16-Channel, 3-Level HV ultrasound transmitter with built-in digital beamformer. Each channel is capable of swinging up to ±80V with an active discharge back to 0V. The outputs can source and sink more than 1.6A to achieve fast output rise and fall times. The active discharge is also capable of ±1.6A for a fast return to ground. The HV7358 additionally features the programmable output current. The output current can be programmed via the I<sup>2</sup>C Interface. All 16 channels have built-in output protection diodes and clamp diodes. The HV7358 features 16 Integrated T/R switches, a receive damping circuit and an active RTZ circuit. The active RTZ circuit has a typical R<sub>ON</sub> of  $300\Omega$ . The active RTZ circuit activates to discharge the transmitter's output internal node when the transmit burst ends.

The gate drivers for the output MOSFETs are powered by built-in linear floating regulators referenced to  $V_{PP}$  and  $V_{NN}$ . This direct coupling topology of the gate drivers eliminates the need for the gate driver and floating power supply circuit.

The HV7358 features an internal low-jitter PLL clock multiplier for generating the delay clock for the built-in digital beamformer. The clock input has to accept an LVDS differential system clock with frequencies from 30 MHz (min.) to 80 MHz (max.) in PLL mode and a frequency from 30 MHz (min.) to 200 MHz (max.) in Non-PLL mode. The clock multiplier is programmable by x1, x2, x3, x4, x5, x6 and x8, and the maximum delay clock frequency can be up to 200 MHz, allowing incremental delays down to 5 ns. This feature eliminates the need for the power-hungry external clock synthesizer/multiplier to generate the high-frequency delay clock from the system/sampling clock. The transmitter outputs are synchronized with the delay clock to reduce phase noise.

#### Package Type

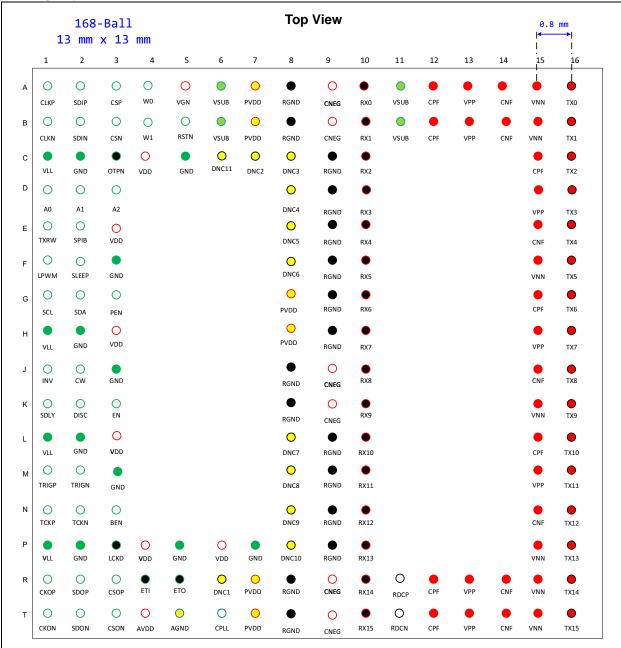

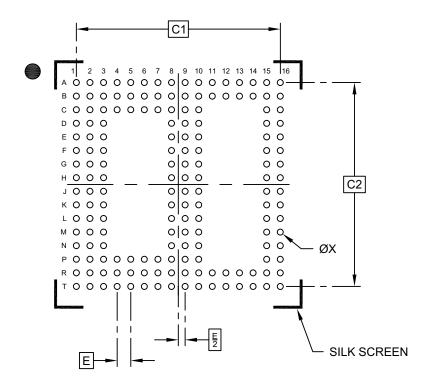

FIGURE 1: HV7358 Pin Configuration.

The 168-lead TFBGA, with an outline 13 mm x 13 mm body, 1.2 mm (max.) height and 0.8 mm pitch package, is available.

Note that the backside of the die bias voltage,  $V_{SUB}$ , must be connected to ground (0V, GND). Because this package is mounted onto a 4 x 4 inch, 4-layer, 1 oz

copper PCB, the maximum allowable power dissipation is about 4W. The maximum junction temperature is lower than +130°C and the package has an ambient temperature of +55°C.

#### **Functional Block Diagram**

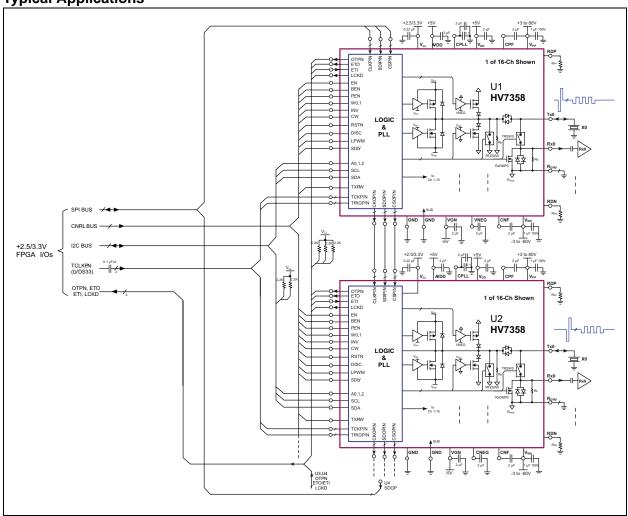

**Typical Applications**

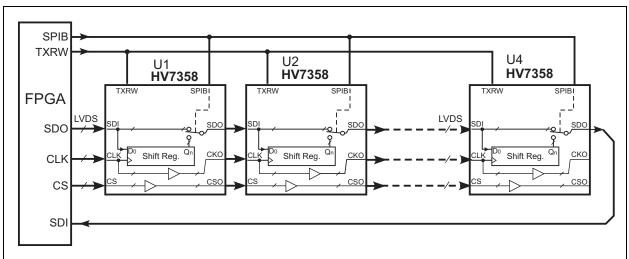

**FIGURE 2:** Multiple HV7358 Devices are Working Together as a 64-Channel Pulser and Beamformer. For More Details about Daisy-Chained SPI Connections, see Figure 4-2 and the Associated Discussion.

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings†

| Substrate (V <sub>SUB</sub> , connect to GND)                                                                          | 0V             |

|------------------------------------------------------------------------------------------------------------------------|----------------|

| All Logic I/O and CLK Pins                                                                                             | 0.5V to +5.5V  |

| Logic Voltage (V <sub>LL</sub> pin has diode to V <sub>DD</sub> and AV <sub>DD</sub> )                                 | 0.5V to +5.5V  |

| Low-Voltage Positive PLL Supply                                                                                        | 0.5V to +5.5V  |

| Low-Voltage Positive Supply                                                                                            | 0.5V to +5.5V  |

| Low-Voltage Positive RTZ Supply                                                                                        | 0.5V to +5.5V  |

| V <sub>GN</sub> Negative Power Supply                                                                                  | 5.5V to +0.5V  |

| V <sub>NEG</sub> Regulator Bypass Cap                                                                                  | 5.5V to +0.5V  |

| V <sub>PLL</sub> Regulator Bypass Cap                                                                                  |                |

| V <sub>PP</sub> Power Supply                                                                                           | 1V to +85V     |

| V <sub>NN</sub> Power Supply                                                                                           |                |

| RDCP V <sub>PP</sub> Rail Bleed Switch <sup>(2)</sup>                                                                  | 1V to +82V     |

| RDCP V <sub>NN</sub> Rail Bleed Switch <sup>(2)</sup>                                                                  | 82V to + -1V   |

| TX <sub>CH</sub> Pin Voltage (no load and all switches off)                                                            | 85V to +85V    |

| RX <sub>CH</sub> Pin to GND Voltage (at I <sub>RX</sub> = ±500 mA DC)                                                  | ±0.7V to ±1.4V |

| Operating Ambient Temperature Range <sup>(1)</sup>                                                                     | 0°C to +85°C   |

| Storage Temperature Range <sup>(1)</sup>                                                                               | 55°C to +150°C |

| Junction Temperature <sup>(1)</sup>                                                                                    | +125°C         |

| High-Voltage Pins HBM (TX0~15, RX0~15, V <sub>PP</sub> , V <sub>NN</sub> , CPF, CNF, RDCP, RDCN pins) <sup>(1,3)</sup> |                |

| Low-Voltage Pins HBM <sup>(1,3)</sup>                                                                                  | 2 kV to +2 kV  |

| Power Dissipation                                                                                                      | 5W             |

| Thermal Resistance Junction to Ambient <sup>(2,4)</sup>                                                                |                |

| Thermal Resistance Junction to PCB <sup>(2,4)</sup>                                                                    |                |

| Thermal Resistance Junction to Case <sup>(2,4)</sup>                                                                   | 2°C/W          |

- Note 1: The design must try to meet the complete range of operating conditions, unless otherwise stated.

- 2: Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

- 3: This device is not required for CDM or MM ESD tests.

- 4: EIA/JESSD51-9, 102 mm x 114 mm x 1.6 mm PCB, Horizontal Still Air, 56 Thermal Vias,  $T_A = +55$ °C,  $T_{,l} = +125$ °C.

- † Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING SUPPLY VOLTAGES**

Unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5.0V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V,  $V_{GN}$  = -5.0V,  $V_{SUB}$  = 0V, EN = PEN = BEN = 1,  $T_A$  = 0° to +85°C

| Parameters                              | Sym.            | Min.  | Тур. | Max.  | Unit | Conditions                                                   |

|-----------------------------------------|-----------------|-------|------|-------|------|--------------------------------------------------------------|

| Positive Logic Supply                   | $V_{LL}$        | 2.375 | 2.50 | 3.625 | V    |                                                              |

| Positive Low-Voltage PLL Supply         | $AV_{DD}$       | 4.75  | 5.0  | 5.25  | V    | AV <sub>DD</sub> , PV <sub>DD</sub> and V <sub>DD</sub> must |

| Positive Low-Voltage RTZ Supply         | $PV_{DD}$       | 4.75  | 5.0  | 5.25  | V    | have separated bypass cap                                    |

| Positive Low-Voltage Supply             | $V_{DD}$        | 4.75  | 5.0  | 5.25  | ٧    | to GND when they are connected to the same +5V               |

| Negative Voltage Supply                 | $V_{GN}$        | -5.25 | -5.0 | -4.75 | V    | B mode and CW mode                                           |

|                                         |                 | _     | 0    | _     |      | V <sub>GN</sub> = 0 (B mode only)                            |

| Positive V <sub>PP</sub> Voltage Supply | $V_{PP}$        | 3.0   | _    | 8.0   | V    | In CW mode                                                   |

|                                         |                 | 8.0   | _    | 80    |      | In B mode                                                    |

| Negative V <sub>NN</sub> Voltage Supply | V <sub>NN</sub> | -8.0  | _    | -3.0  |      | In CW mode                                                   |

|                                         |                 | -80   | _    | -8.0  |      | In B mode                                                    |

**Note:** The device is not ensured to function outside the operating range.

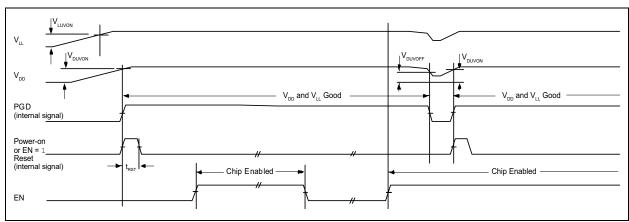

#### POWER-UP AND POWER-DOWN SEQUENCES

Powering up/down in any arbitrary sequence will not cause any damage to the device. The powering up/down sequences are only recommended in order to minimize possible inrush current.

| Step | Power-up Description                             | Step | Power-Down Description                            |

|------|--------------------------------------------------|------|---------------------------------------------------|

| 1    | V <sub>LL</sub> On with Logic Signal Low         | 1    | EN = 0 and the Logic Control Signal goes to Low   |

| 2    | $AV_{DD}$ , $PV_{DD}$ , $V_{DD}$ and $V_{GN}$ On | 2    | V <sub>PP</sub> and V <sub>NN</sub> Off           |

| 3    | V <sub>PP</sub> and V <sub>NN</sub> On           | 3    | $AV_{DD}$ , $VP_{DD}$ , $V_{DD}$ and $V_{GN}$ Off |

| 4    | EN = 1 and Logic Control Signal Active           | 4    | V <sub>LL</sub> Off                               |

**Note:** The HV7358 is a high-voltage CMOS I<sup>2</sup>C with multiple supply rails. It is highly recommended to add a Schottky diode at each voltage rail to GND, with 2~3A and sufficient BV, on the same PCB device(s) in mounted. Only one set of such diodes is needed per PCB.

### **ELECTRICAL SPECIFICATIONS**

| LIN - 1, SFIB - BLIN - 0, 1A - +2                    |                       |       |       |      |       |                                                                           |

|------------------------------------------------------|-----------------------|-------|-------|------|-------|---------------------------------------------------------------------------|

| Parameters                                           | Sym.                  | Min.  | Тур.  | Max. | Units | Conditions                                                                |

| V <sub>LL</sub> Quiescent Current                    | I <sub>LLQ</sub>      | _     | 2.0   | 7.0  | μΑ    | EN = PEN = 0,                                                             |

| AV <sub>DD</sub> Quiescent Current                   | I <sub>AVDDQ</sub>    | _     | 0.5   | 5.0  |       | $f_{TCK} = f_{CLK} = 0 \text{ MHz}$                                       |

| V <sub>DD</sub> Quiescent Current                    | $I_{\mathrm{DDQ}}$    | _     | 58    | 75   |       |                                                                           |

| PV <sub>DD</sub> Quiescent Current                   | $I_{PVDDQ}$           |       | 6.0   | 15   |       |                                                                           |

| V <sub>GN</sub> Quiescent Current                    | $I_{GNQ}$             | -5.0  | -2.2  |      |       |                                                                           |

| V <sub>PP</sub> Quiescent Current                    | $I_{PPQ}$             | _     | 2.0   | 8.0  |       |                                                                           |

| V <sub>NN</sub> Quiescent Current                    | I <sub>NNQ</sub>      | -14   | -7.0  |      |       |                                                                           |

| V <sub>LL</sub> Current at Chip Enabled              | I <sub>LLEN</sub>     | _     | 0.01  | 0.1  | mA    | EN = 1, $PEN = 0$ ,                                                       |

| AV <sub>DD</sub> Current at Chip Enabled             | I <sub>AVDDEN</sub>   | _     | 0.3   | 1.5  |       | $f_{TCK} = f_{CLK} = 0 \text{ MHz}$                                       |

| V <sub>DD</sub> Current at Chip Enabled              | I <sub>DDEN</sub>     | _     | 1.35  | 3.0  |       |                                                                           |

| PV <sub>DD</sub> Current at Chip Enabled             | I <sub>PVDDEN</sub>   | _     | 0.2   | 1.5  |       |                                                                           |

| V <sub>GN</sub> Current at Chip Enabled              | I <sub>VGNEN</sub>    | -1.5  | -0.2  | _    |       |                                                                           |

| V <sub>PP</sub> Current at Chip Enabled              | I <sub>PPEN</sub>     | _     | 0.1   | 1.0  |       |                                                                           |

| V <sub>NN</sub> Current at Chip Enabled              | I <sub>NNEN</sub>     | -0.75 | -0.67 | _    |       |                                                                           |

| AV <sub>DD</sub> Current with PLL and Buffer Enabled | I <sub>AVDD_PLL</sub> | _     | 4.7   | 8.0  | mA    | EN = PEN = BEN = 1,<br>$f_{TCK}$ = 40 MHz, $f_C$ = 160 MHz <sup>(1)</sup> |

| V <sub>LL</sub> CW Current                           | I <sub>LLCW</sub>     | _     | 3.0   | 10   | mA    | TX <sub>CH</sub> one-channel output 5 MHz,                                |

| AV <sub>DD</sub> CW Current                          | I <sub>AVDDCW</sub>   | _     | 0.5   | 2.0  |       | continuous, no loads, CW = 1,                                             |

| V <sub>DD</sub> CW Current                           | I <sub>DDCW</sub>     | _     | 8.0   | 15   |       | CWOC = 1, $V_{PP}/V_{NN} = \pm 5V^{(1)}$                                  |

| PV <sub>DD</sub> CW Current                          | I <sub>PVDDCW</sub>   | _     | 1.45  | 5.0  |       |                                                                           |

| V <sub>GN</sub> CW Current                           | I <sub>GNCW</sub>     | -10   | -4.6  | _    | mA    | TX <sub>CH</sub> one-channel output 5 MHz,                                |

| V <sub>PP</sub> CW Current                           | I <sub>PPCW</sub>     | _     | 13    | 18   |       | continuous, no loads, CW = 1,<br>CWOC = 1, $V_{PP}/V_{NN} = \pm 5V^{(1)}$ |

| V <sub>NN</sub> CW Current                           | I <sub>NNCW</sub>     | -18   | -10.5 | _    |       | CVVOC = 1, V <sub>PP</sub> /V <sub>NN</sub> = ±5V <sup>C</sup> /          |

**Note 1:** Characterized only; not 100% tested in production.

TABLE 1-1: TX<sub>CH</sub> OUTPUT P-CHANNEL MOSFET ON V<sub>PP</sub>

| Parameters                       | Sym.                | Min. | Тур. | Max. | Units | Conditions                                    |

|----------------------------------|---------------------|------|------|------|-------|-----------------------------------------------|

| B mode Output Current, BOC = 00b | I <sub>OUT_P</sub>  | _    | 0.9  | _    | Α     | $V_{PP} = +25V$ , $R_L = 1\Omega$ to GND,     |

| B mode Output Current, BOC = 01b |                     | _    | 0.6  | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup> |

| B mode Output Current, BOC = 10b |                     | _    | 0.3  | _    |       | D% = 0.1%(*)                                  |

| B mode Output Current, BOC = 11b |                     | _    | 0.15 | _    |       |                                               |

| B mode Output Current, BOC = 00b |                     | _    | 1.6  | _    |       | $V_{PP}$ = +80V, $R_L$ = 1 $\Omega$ to GND,   |

| B mode Output Current, BOC = 01b |                     | _    | 1.1  | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup> |

| B mode Output Current, BOC = 10b |                     | _    | 0.6  | _    |       | D% = 0.1%(*)                                  |

| B mode Output Current, BOC = 11b |                     | _    | 0.3  | _    |       |                                               |

| On-Resistance B mode, BOC = 00b  | R <sub>ONB_P</sub>  | _    | 12   | _    | Ω     | I <sub>SD</sub> = 100 mA <sup>(1)</sup>       |

| On-Resistance, CW = 1, CWOC = 0  | R <sub>ONCW_P</sub> | _    | 36   | _    |       | At $V_{PP} = +5V^{(1)}$                       |

| On-Resistance, CW = 1, CWOC = 1  |                     | _    | 50   | _    |       |                                               |

**Note 1:** Characterized only; not 100% tested in production.

TABLE 1-2: TX<sub>CH</sub> OUTPUT N-CHANNEL MOSFET ON V<sub>NN</sub>

| Parameters                       | Sym.                | Min. | Тур.  | Max. | Units | Conditions                                    |

|----------------------------------|---------------------|------|-------|------|-------|-----------------------------------------------|

| B mode Output Current, BOC = 00b | I <sub>OUT_N</sub>  | -    | -1.0  | _    | Α     | $V_{NN}$ = -25V, $R_L$ = 1 $\Omega$ to GND,   |

| B mode Output Current, BOC = 01b |                     | _    | -0.7  | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup> |

| B mode Output Current, BOC = 10b |                     | _    | -0.36 | _    |       | D% = 0.1%(*)                                  |

| B mode Output Current, BOC = 11b |                     | _    | -0.18 | _    |       |                                               |

| B mode Output Current, BOC = 00b |                     | _    | -1.6  | _    |       | $V_{NN}$ = -80V, $R_L$ = 1 $\Omega$ to GND,   |

| B mode Output Current, BOC = 01b |                     | _    | -1.0  | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup> |

| B mode Output Current, BOC = 10b |                     | _    | -0.5  | _    |       | D% = 0.1%(*)                                  |

| B mode Output Current, BOC = 11b |                     | _    | -0.3  | _    |       |                                               |

| On-Resistance B mode, BOC = 11b  | R <sub>ONB_N</sub>  | _    | 10.5  | _    | Ω     | I <sub>SD</sub> = 100 mA <sup>(1)</sup>       |

| On-Resistance, CW = 1, CWOC = 0  | R <sub>ONCW_N</sub> | _    | 42    | _    |       | At $V_{NN} = -5V^{(1)}$                       |

| On-Resistance, CW = 1, CWOC = 1  | _                   | _    | 59    | _    |       |                                               |

**Note 1:** Characterized only; not 100% tested in production.

TABLE 1-3: TX<sub>CH</sub> DAMPING P-CHANNEL MOSFET ON GND

| - 011                            |                       |      |      |      |           |                                                  |

|----------------------------------|-----------------------|------|------|------|-----------|--------------------------------------------------|

| Parameters                       | Sym.                  | Min. | Тур. | Max. | Unit<br>s | Conditions                                       |

| B mode Output Current, BOC = 00b | I <sub>OUT_PDMP</sub> | _    | 1.7  | _    | Α         | $R_L = 1\Omega$ , $TX_{CH}$ to $V_{NN} = -25V$ , |

| B mode Output Current, BOC = 01b | _                     | _    | 1.2  | _    |           | 20 ns pulse width at D% = 0.1% <sup>(1)</sup>    |

| B mode Output Current, BOC = 10b |                       | _    | 0.6  | _    |           | D% = 0.1%(*)                                     |

| B mode Output Current, BOC = 11b |                       | _    | 0.3  | _    |           |                                                  |

| B mode Output Current, BOC = 00b |                       | _    | 2.3  | _    |           | $R_L = 1\Omega$ , $TX_{CH}$ to $V_{NN} = -80V$ , |

| B mode Output Current, BOC = 01b |                       | _    | 1.5  | _    |           | 20 ns pulse width at D% = 0.1% <sup>(1)</sup>    |

| B mode Output Current, BOC = 10b |                       | _    | 8.0  | _    |           | D% = 0.1%(*)                                     |

| B mode Output Current, BOC = 11b |                       | _    | 0.4  | _    |           |                                                  |

| On-Resistance                    | R <sub>ON_PDMP</sub>  | _    | 8.1  | _    | Ω         | I <sub>SD</sub> = 100 mA <sup>(1)</sup>          |

Note 1: Characterized only; not 100% tested in production.

TABLE 1-4: TX<sub>CH</sub> DAMPING N-CHANNEL MOSFET ON GND

| Parameters                       | Sym.                  | Min. | Тур. | Max. | Units | Conditions                                       |

|----------------------------------|-----------------------|------|------|------|-------|--------------------------------------------------|

| B mode Output Current, BOC = 00b | I <sub>OUT_NDMP</sub> | _    | -1.6 | _    | Α     | $R_L = 1\Omega$ , $TX_{CH}$ to $V_{PP} = +25V$ , |

| B mode Output Current, BOC = 01b |                       | _    | -1.0 | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup>    |

| B mode Output Current, BOC = 10b |                       | _    | -0.5 | _    |       |                                                  |

| B mode Output Current, BOC = 11b |                       | _    | -0.3 | _    |       |                                                  |

| B mode Output Current, BOC = 00b |                       | _    | -2.3 | _    |       | $R_L = 1\Omega$ , $TX_{CH}$ to $V_{PP} = +80V$ , |

| B mode Output Current, BOC = 01b |                       | _    | -1.5 | _    |       | 20 ns pulse width at D% = 0.1% <sup>(1)</sup>    |

| B mode Output Current, BOC = 10b |                       | _    | -0.8 | _    |       |                                                  |

| B mode Output Current, BOC = 11b |                       | _    | -0.4 | _    |       |                                                  |

| On-Resistance                    | R <sub>ON_NDMP</sub>  | _    | 4.2  | _    | Ω     | I <sub>SD</sub> = 100 mA <sup>(1)</sup>          |

Note 1: Characterized only; not 100% tested in production.

TABLE 1-5: RTZ AUTO-BLEED AND V<sub>PP</sub>/V<sub>NN</sub> SUPPLY RAIL BLEED SWITCHES

| Parameters                                       | Sym.               | Min. | Тур. | Max. | Units | Conditions                               |

|--------------------------------------------------|--------------------|------|------|------|-------|------------------------------------------|

| RTZSW On-Resistance                              | R <sub>RTZSW</sub> | _    | 190  | _    | Ω     | $I_{SD} = \pm 1.0 \text{ mA}^{(1)}$      |

| Bleed Resistor to GND per Channel <sup>(1)</sup> | $R_b$              | _    | 17   | _    | kΩ    |                                          |

| RTZSW Off Withstand Voltage                      | V <sub>RTZSW</sub> | -80  | _    | +80  | V     | I <sub>SW</sub> = ±100 μA <sup>(1)</sup> |

| RDCP Switch Output Current                       | I <sub>RDCP</sub>  |      | 5.8  | _    | mA    | $V_{PP} = +80V^{(1)}$                    |

| RDCN Switch Output Current                       | I <sub>RDCN</sub>  |      | -6.0 | _    |       | $V_{NN} = -80V^{(1)}$                    |

| Voltage of RDCP                                  | $V_{RDCP}$         | 0    |      | +82  | V     | $I_{RDCP/N} = \pm 0.6A_{(PK)}^{(1)}$     |

| Voltage of RDCN Bleed Pin for V <sub>NN</sub>    | $V_{RDCN}$         | -82  |      | 0    |       |                                          |

| Suggested Bleed Resistor Value to                | R <sub>DCP</sub>   |      | 1.0  | _    | kΩ    | An external resistor (0.25W)             |

| GND for RDCP and RDCN Pins                       | R <sub>DCN</sub>   |      | 1.0  |      |       | for pin to GND suggested <sup>(2)</sup>  |

Note 1: Characterized only; not 100% tested in production.

TABLE 1-6: TX<sub>CH</sub> OUTPUT ISOLATION DIODES AND BLEED RESISTOR

| Parameters                                | Sym.             | Min. | Тур. | Max. | Units | Conditions                            |

|-------------------------------------------|------------------|------|------|------|-------|---------------------------------------|

| Diode Forward Voltage                     | V <sub>F</sub>   | _    | 1.2  | _    | V     | I <sub>FM</sub> = 300 mA              |

| Forward Continuous Current <sup>(1)</sup> | I <sub>FM</sub>  | _    | 300  | _    | mA    |                                       |

| Peak Forward Pulse Current                | I <sub>FSM</sub> | _    | 3.0  | _    | Α     | PW = 50 ns <sup>(1)</sup>             |

| Total Capacitance of Diode Pair           | C <sub>T</sub>   | _    | 3.5  | _    | pF    | At 1 MHz, 1 dBm, 0V DC <sup>(1)</sup> |

Note 1: Characterized only; not 100% tested in production.

<sup>2:</sup> Design guidance only.

TABLE 1-7: TRSW AND RXDMP SWITCHES

| Parameters                                            | Sym.               | Min. | Тур. | Max. | Units | Conditions                               |

|-------------------------------------------------------|--------------------|------|------|------|-------|------------------------------------------|

| TRSW Analog Switch-On Resistor                        | R <sub>TRSW</sub>  | _    | 17   | 22   | Ω     | I <sub>TRSW</sub> = ±1 mA <sup>(1)</sup> |

| TRSW Off Withstand Voltage                            | $V_{TRSW}$         | -80  | _    | +80  | V     | $I_{SW} = \pm 100  \mu A^{(1)}$          |

| RX <sub>CH</sub> to GND Protection Diode              | V <sub>F</sub>     | _    | ±0.8 | ±1.2 | V     | $I_F = \pm 20 \text{ mA}^{(1)}$          |

| RXDMP Switch-On Resistance                            | R <sub>RXDMP</sub> | _    | 15   | _    | Ω     | $I_{SD} = \pm 1 \text{ mA}^{(1)}$        |

| RX <sub>CH</sub> Bleed Resistor to GND <sup>(1)</sup> | R <sub>b</sub>     | _    | 17   | _    | kΩ    |                                          |

| RX <sub>CH</sub> Pin to GND Capacitance               | C <sub>RXG</sub>   | _    | _    | 7.0  | pF    | At 1 MHz, 1 dBm, 0V DC <sup>(2)</sup>    |

Note 1: Characterized only; not 100% tested in production.

2: Design guidance only.

TABLE 1-8: BUILT-IN VOLTAGE LINEAR REGULATORS

Unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V,  $V_{GN}$  = -5V,  $V_{SUB}$  = 0V, EN = 1, PEN = BEN = 0,  $V_{AB}$  = +25°C

| FEIN - BEIN - 0, 1A - +23 C                                          |                    |      | 1    |      |       | 1                                                    |

|----------------------------------------------------------------------|--------------------|------|------|------|-------|------------------------------------------------------|

| Parameters                                                           | Sym.               | Min. | Тур. | Max. | Units | Conditions                                           |

| Output P-Channel Gate Drive<br>Voltage Referenced to V <sub>PP</sub> | $V_{PF}$           | -4.9 | -5.0 | -5.1 | V     | $(V_{GN} - V_{PP}) < -8.0V$                          |

| Output N-Channel Gate Drive<br>Voltage Referenced to V <sub>NN</sub> | V <sub>NF</sub>    | 5.1  | 5.0  | 5.3  | V     | $(V_{DD} - V_{NN}) > +8.0V$                          |

| Output P-Channel Gate Drive Voltage Referenced to GND                | V <sub>NEG</sub>   | -5.1 | -5.0 | -4.9 | V     | CW = 0                                               |

| Output PLL Voltage Referenced to GND                                 | V <sub>PLL</sub>   | 4.4  | 4.6  | 4.8  | V     | PEN = 1                                              |

| Dropout Voltage of (V <sub>PP</sub> – V <sub>GN</sub> )              | $V_{DOPF}$         | _    | 3.5  | _    | V     | 100 mA load, drop to 95% at                          |

| Dropout Voltage of (V <sub>DD</sub> – V <sub>NN</sub> )              | $V_{DONF}$         | _    | 3.5  | _    | V     | worst case <sup>(1)</sup>                            |

| Dropout Voltage of (V <sub>NEG</sub> – V <sub>NN</sub> )             | $V_{DONEG}$        | _    | 1.36 | _    | V     | 10 mA load, drop to 95% at worst case <sup>(1)</sup> |

| Dropout Voltage of (AV <sub>DD</sub> – V <sub>PLL</sub> )            | V <sub>DOPLL</sub> | _    | 0.31 | _    | V     | 1 mA load, drop to 95% at worst case <sup>(1)</sup>  |

Note 1: Characterized only; not 100% tested in production.

TABLE 1-9: LOGIC INPUTS CHARACTERISTICS

| Parameters                                 | Sym.              | Min. | Тур. | Max.                | Units | Conditions                                                                           |

|--------------------------------------------|-------------------|------|------|---------------------|-------|--------------------------------------------------------------------------------------|

| Rise/Fall Time of Input Logic Signals      | t <sub>rf</sub>   | _    | _    | 3.5                 | ns    | 10% to 90% at pin(s)(2)                                                              |

| Input Logic Low Voltage <sup>(1)</sup>     | V <sub>IL</sub>   | 0    | _    | 0.2 V <sub>LL</sub> | V     |                                                                                      |

| Input Logic High Voltage <sup>(1)</sup>    | V <sub>IH</sub>   | 0.8  | _    | $V_{LL}$            | V     |                                                                                      |

| Input Logic Low Current                    | I <sub>IL</sub>   | -0.1 | _    | _                   | μΑ    |                                                                                      |

| Input Logic High Current                   | I <sub>IH</sub>   | _    | _    | 1.0                 | μΑ    |                                                                                      |

| Input Capacitance <sup>(2)</sup>           | C <sub>IN</sub>   | _    | 2.0  | 3.0                 | pF    |                                                                                      |

| EN Switching On Time                       | t <sub>EN</sub>   | _    | 300  | _                   | μs    | 50% EN rise to TX <sub>CH</sub> ready <sup>(2)</sup>                                 |

| EN Switching Off Time                      |                   | _    | 300  | _                   | ns    | 50% EN fall to TX <sub>CH</sub> , all output FETs on HV rails are off <sup>(1)</sup> |

| Internal Reset Signal Width <sup>(2)</sup> | t <sub>RST</sub>  | 100  | _    | 150                 | ns    |                                                                                      |

| Reset Input Low Time <sup>(1)</sup>        | t <sub>RSTN</sub> | 100  |      | _                   | ns    |                                                                                      |

Note 1: Characterized only; not 100% tested in production.

2: Design guidance only.

TABLE 1-10: OVERTEMPERATURE AND UNDERVOLTAGE PROTECTIONS

| Parameters                           | Sym.                  | Min. | Тур. | Max. | Units | Conditions                                    |  |

|--------------------------------------|-----------------------|------|------|------|-------|-----------------------------------------------|--|

| OTP Output Maximum Pull-up           | V <sub>OH</sub>       | _    | _    | 5.25 | V     |                                               |  |

| OTP Output Low Maximum Voltage       | V <sub>OL</sub>       |      | _    | 0.1  | V     | At 100 μA                                     |  |

|                                      |                       |      | _    | 0.4  | ٧     | At 4 mA                                       |  |

| OTP Output High Current              | I <sub>OFF</sub>      | _    | _    | 10   | μΑ    | 0° to +125°C, at 5.25V pull-up <sup>(1)</sup> |  |

| Thermal Shutdown Trip Point          | T <sub>TRIP</sub>     | +135 | _    | +155 | °C    | OTP = H when thermal                          |  |

| Thermal Shutdown Hysteresis          | T <sub>HYS</sub>      |      | 40   | _    |       | shutdown occurs <sup>(1)</sup>                |  |

| V <sub>DD</sub> Ok Voltage           | $V_{DDUVON}$          | 3.9  | 4.2  | 4.5  | V     | External power supply                         |  |

| V <sub>DD</sub> UVLO Trip Voltage    | $V_{DDUVOFF}$         | 3.7  | 3.95 | 4.3  |       | inputs <sup>(1)</sup>                         |  |

| V <sub>LL</sub> Ok Voltage           | $V_{LLUVON}$          | 1.65 | 1.75 | 1.85 |       |                                               |  |

| V <sub>LL</sub> UVLO Trip Voltage    | $V_{LLUVOFF}$         | 1.5  | 1.6  | 1.7  |       |                                               |  |

| V <sub>PLL</sub> Ok Voltage          | $V_{PLLUVON}$         |      | 3.8  | _    |       | +4.5V LR for PLL circuit <sup>(1)</sup>       |  |

| V <sub>PLL</sub> UVLO Trip Voltage   | V <sub>PLLUVOFF</sub> |      | 3.3  | _    |       |                                               |  |

| V <sub>NEG</sub> Ok Voltage          | $V_{NGUVON}$          |      | -4.0 |      |       | -5V LR for RTZ P-FET gate                     |  |

| V <sub>NEG</sub> UVLO Trip Voltage   | $V_{NGUVOFF}$         |      | -4.4 | _    |       | drive circuit <sup>(1)</sup>                  |  |

| V <sub>PP-PF</sub> Ok Voltage        | $V_{PP-PFON}$         |      | -3.4 | _    | ٧     | Floating ±5V LRs for HV                       |  |

| V <sub>PP-PF</sub> UVLO Trip Voltage | V <sub>PP-PFOFF</sub> |      | -3.8 | _    |       | P-FET and N-FET gate drive                    |  |

| V <sub>NF-NN</sub> Ok Voltage        | V <sub>NF-NNON</sub>  | _    | 3.8  | _    |       | circuit                                       |  |

| V <sub>NF-NN</sub> UVLO Trip Voltage | V <sub>NF-NNOFF</sub> | _    | 3.4  | _    |       |                                               |  |

Note 1: Characterized only; not 100% tested in production.

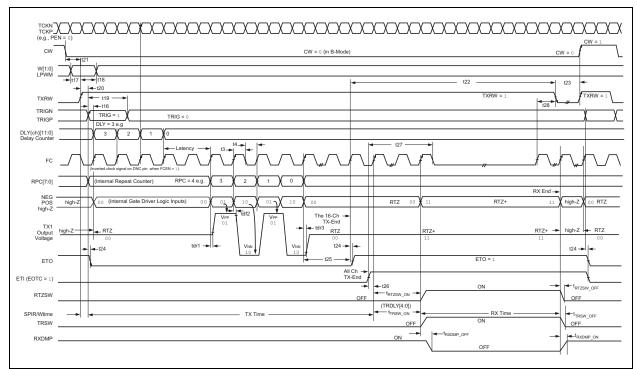

TABLE 1-11: SWITCH TIMING CHARACTERISTICS

Unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V,  $V_{GN}$  = -5V,  $V_{SUB}$  = 0V, EN = 1, PEN = BEN = 0,  $V_{AB}$  = +25°C

| $PEN = BEN = 0, I_A = +25^{\circ}C$                                 |                         |         | 1              |          | Units | T                                                                                                            |

|---------------------------------------------------------------------|-------------------------|---------|----------------|----------|-------|--------------------------------------------------------------------------------------------------------------|

| Parameters                                                          | Sym.                    | Min.    | Min. Typ. Max. |          |       | Conditions                                                                                                   |

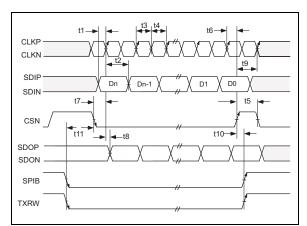

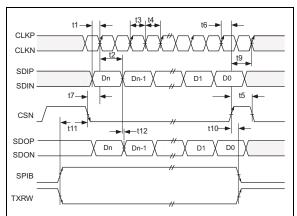

| SDI Valid to CLK Setup Time <sup>(1)</sup>                          | t <sub>1</sub>          | 2.0     | _              | _        | ns    |                                                                                                              |

| CLKP to SDI Data Hold Time <sup>(1)</sup>                           | t <sub>2</sub>          | 2.0     | _              | _        | ns    |                                                                                                              |

| CLK High Time % of 1/f <sub>CLK</sub> <sup>(1)</sup>                | t <sub>3</sub>          | 45      | _              | 55       | %     |                                                                                                              |

| CLK Low Time % of 1/f <sub>CLK</sub> <sup>(1)</sup>                 | t <sub>4</sub>          | 45      | _              | 55       | %     |                                                                                                              |

| CSN Minimum High Time Between SPI Words                             | t <sub>5</sub>          |         | 3-cycle        |          | CLK   | Designed for f <sub>CLK</sub> = 200 MHz <sup>(2)</sup>                                                       |

| CLKP Rise to CSN Rise <sup>(1)</sup>                                | t <sub>6</sub>          | _       | 2.0            | _        | ns    |                                                                                                              |

| CSON Fall to CLKP Rise <sup>(1)</sup>                               | t <sub>7</sub>          | _       | 2.0            | _        | ns    |                                                                                                              |

| SDOP Delay from CLKP Rise                                           | t <sub>8</sub>          | _       | 2.0            | 3.0      | ns    | SPIB = 0, 3 pF Load <sup>(1)</sup>                                                                           |

| CSN Rise to CLK Rise <sup>(1)</sup>                                 | t <sub>9</sub>          | _       | 2.0            | _        | ns    |                                                                                                              |

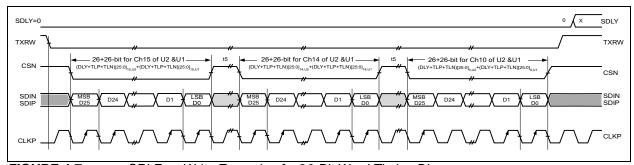

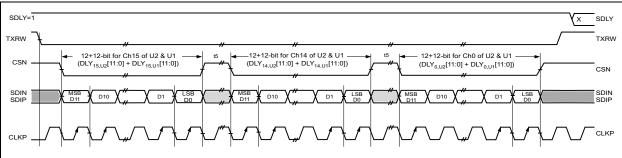

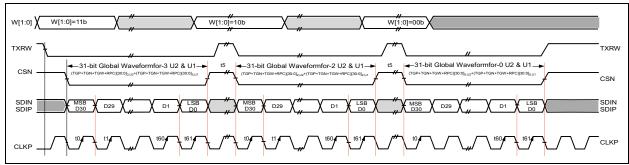

| CSN Rise to TXRW or to SPIB(2)                                      | t <sub>10</sub>         |         | 9-cycle        |          | TCK   |                                                                                                              |

| CLK Start, TXRW, SPIB to CSN Fall(2)                                | t <sub>11</sub>         | _       | 200            | _        | ns    |                                                                                                              |

| SDIP to SDOP Delay                                                  | t <sub>12</sub>         | _       | 10             | _        | ns    | SPIB = 1, 3 pF Load <sup>(1)</sup>                                                                           |

| TXRW Rise to CLKP Rise Edge <sup>(1)</sup>                          | t <sub>13</sub>         | _       | 6.0            | _        | ns    |                                                                                                              |

| TX <sub>CH</sub> Ready Latency after TXRW = 1 <sup>(2)</sup>        | t <sub>14</sub>         |         | 12-cycle       | e        | TCK   |                                                                                                              |

| SPI or I <sup>2</sup> C Ready after TXRW = 0 <sup>(2)</sup>         | t <sub>15</sub>         |         | 2-cycle        |          | TCK   |                                                                                                              |

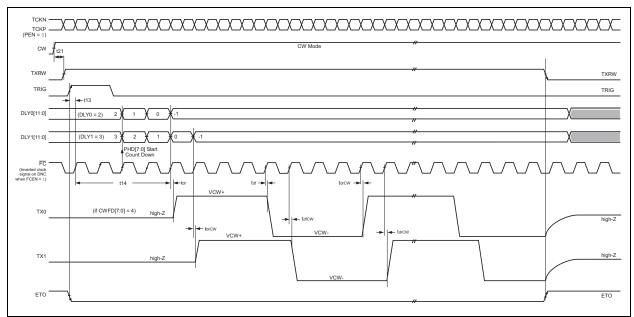

| TRIG Rise to CLK Rise Setup Time                                    | t <sub>16</sub>         |         | 0.5-cycle      | е        | ns    |                                                                                                              |

| W0 or W1 Pin Ready to TXRW Rise Time                                | t <sub>17</sub>         |         | 3-cycle        |          | ns    |                                                                                                              |

| W0 or W1 Pin Holdup Time                                            | t <sub>18</sub>         |         | 3-cycle        |          | ns    |                                                                                                              |

| TRIG High Time <sup>(2)</sup>                                       | t <sub>19</sub>         |         | 6-cycle        |          | TCK   |                                                                                                              |

| TXRW Rise to TRIG Rise Time                                         | t <sub>20</sub>         |         | 3-cycle        |          | ns    |                                                                                                              |

| CW Pin Changing to TXRW Rise Time                                   | t <sub>21</sub>         |         | 3-cycle        |          | ns    | Mode changing time <sup>(2)</sup>                                                                            |

| ETO High to TXRW High or Low Time                                   | t <sub>22</sub>         | 2.0     |                | 10       | ns    |                                                                                                              |

| Minimum TXRW Low Time                                               | t <sub>23</sub>         |         | 1.2            |          | μs    | Must wait for the TRSW to completely turn off <sup>(2)</sup>                                                 |

| This Chip ETO Change Time <sup>(1)</sup>                            | t <sub>24</sub>         | ı       | 45             |          | ns    |                                                                                                              |

| f <sub>C</sub> Clock Cycles before ETO Rise <sup>(1)</sup>          | t <sub>25</sub>         |         | 11-cycle       | 9        | TCK   |                                                                                                              |

| ETI High to f <sub>C</sub> Clock Rise Setup Time <sup>(1)</sup>     | t <sub>26</sub>         |         | 0.5-cycle      | е        | ns    |                                                                                                              |

| Minimum TCK Cycles after ETI Rise                                   | t <sub>27</sub>         | TRDL    | Y[4:0] + (     | 6-cycle) | TCK   | Stop TCK for power saving in                                                                                 |

| Minimum TCK Cycles before TXRW = 0                                  | t <sub>28</sub>         |         | 6-cycle        |          | TCK   | RX <sub>CH</sub> time <sup>(2)</sup>                                                                         |

| Delay Finish to TX <sub>CH</sub> Launch Latency Time <sup>(2)</sup> | t <sub>Latency</sub>    | 5-cycle |                |          | TCK   |                                                                                                              |

| SPI Data Clock Resynchronization Time <sup>(2)</sup>                | t <sub>Sync</sub>       |         | 32-cycle       | 9        | CLK   |                                                                                                              |

| Second Harmonic Distortion                                          | HD2                     |         | -43            | -40      | dB    | HD2 at 5 MHz, 5-cycle pulse                                                                                  |

| Output Rise Time from 0V to V <sub>PP</sub>                         | t <sub>r</sub>          |         | 12             | 14       | ns    | inversion, ±70V, in 100 μs appart,                                                                           |

| Output Fall Time from 0V to V <sub>NN</sub>                         | t <sub>f</sub>          | _       | 12             | 14       | ns    | 220 pF/2.5k Load.                                                                                            |

| Output Rise Time from V <sub>NN</sub> to V <sub>PP</sub>            | t <sub>r2</sub> — 24 26 |         |                | 26       | ns    | The t <sub>r</sub> , t <sub>f</sub> , t <sub>dr</sub> , t <sub>df</sub> values, at ±70V, 220 pF //2.5k Load. |

| Output Fall Time from V <sub>PP</sub> to V <sub>NN</sub>            | t <sub>f2</sub>         |         |                |          | ns    | ZZO pi //Z.ok Lodu.                                                                                          |

| Propagation Delay Rise Time 1                                       | t <sub>dr</sub>         | _ 20 _  |                |          | ns    |                                                                                                              |

| Propagation Delay Fall Time 1                                       | t <sub>df</sub>         |         | 20             | _        | ns    |                                                                                                              |

| Delay Time Matching                                                 | Δt <sub>d</sub>         | _       | ±1.0           | _        | ns    | P to N, channel to channel<br>matching in IC, at ±70V,<br>220 pF //2.5k Load <sup>(1)</sup>                  |

Note 1: Characterized only; not 100% tested in production.

2: Design guidance only.

TABLE 1-12: SPI AND I<sup>2</sup>C I/O CHARACTERISTICS

Unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V,  $V_{GN}$  = -5V,  $V_{SUB}$  = 0V, EN = 1,  $T_A$  = +25°C

| Parameters                                                      | Sym.                  | Min.                     | Тур.               | Max.                     | Units | Conditions                                 |  |  |

|-----------------------------------------------------------------|-----------------------|--------------------------|--------------------|--------------------------|-------|--------------------------------------------|--|--|

| LVDS Differential Input: CLKP/N, SDIP/N, CSP/N and TRIGP/N Pins |                       |                          |                    |                          |       |                                            |  |  |

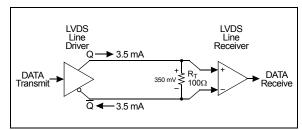

| SPI LVDS Clock I/O Frequency                                    | f <sub>CLK</sub>      | 30                       | _                  | 200                      | MHz   |                                            |  |  |

| SPI LVDS Clock Input Duty Cycle <sup>(1)</sup>                  | D%                    | 45                       | 50                 | 55                       | %     |                                            |  |  |

| AC Differential Sensitivity                                     | V <sub>SNS</sub>      | 150                      | 200                | _                        | mV    | P-P at 200 MHz <sup>(1)</sup>              |  |  |

| AC Common-Mode Voltage <sup>(1)</sup>                           | $V_{CMAC}$            | 1                        | _                  | 1.4                      | V     |                                            |  |  |

| DC Common-Mode Voltage                                          | $V_{REF}$             | $V_{LL}/2 - 0.2$         | V <sub>LL</sub> /2 | $V_{LL}/2 + 0.2$         | V     |                                            |  |  |

| CLK Input Offset Voltage <sup>(1)</sup>                         | V <sub>OFFSET</sub>   | _                        | 30                 | _                        | mV    |                                            |  |  |

| LVDS DC Input Differential Voltage                              | $V_{ID}$              | 100                      | 350                | 600                      | mV    | Same as FPGA I/O                           |  |  |

| CLK Input Resistance                                            | R <sub>IN_CLK</sub>   | _                        | 5.0                | _                        | kΩ    |                                            |  |  |

| CLK Input Capacitance <sup>(2)</sup>                            | C <sub>IN_CLK</sub>   | _                        | 4.0                | _                        | pF    |                                            |  |  |

| CLK Input Bias Current                                          | I <sub>BIAS_CLK</sub> | _                        | 1.0                | _                        | mA    | At input 200 mVp-p                         |  |  |

| LVDS Differential Output: CKOP/N, S                             | DOP/N and             | CSOP/N Pir               | าร                 |                          |       |                                            |  |  |

| LVDS DC Output Differential Voltage                             | V <sub>OD</sub>       | 300                      | 500                | _                        | mV    | $R_T = 100\Omega$ ,                        |  |  |

| LVDS DC Output Common-Mode<br>Voltage                           | V <sub>OCM</sub>      | V <sub>LL</sub> /2 – 0.2 | V <sub>LL</sub> /2 | V <sub>LL</sub> /2 + 0.2 | V     | termination resistor<br>at the P to N LVDS |  |  |

| LVDS Output High Voltage for P&N Pins                           | V <sub>OH</sub>       | _                        | 1.38               | 1.6                      | V     | input pins <sup>(2)</sup>                  |  |  |

| LVDS Output Low Voltage for P&N Pins                            | V <sub>OL</sub>       | 0.9                      | 1.03               | _                        | V     |                                            |  |  |

| Output Current for P&N Pins                                     | I <sub>O_LVDS</sub>   | ±3.0                     | ±3.5               | ±5.0                     | mA    |                                            |  |  |

| Output Rise Time                                                | t <sub>RO</sub>       | _                        | 1.5                | _                        | ns    |                                            |  |  |

| Output Fall Time                                                | t <sub>FO</sub>       | _                        | 1.5                | _                        | ns    |                                            |  |  |

| CKOP/N Output Clock Duty Cycle                                  | D% <sub>CKO</sub>     | 49.5                     | 50                 | 50.5                     | %     | At 200 MHz <sup>(2)</sup>                  |  |  |

| Output Rise Propagation Delay                                   | t <sub>DRO</sub>      | _                        | 1.5                | 2.0                      | ns    | CKOP 50% to CKN                            |  |  |

| Output Fall Propagation Delay t <sub>DF0</sub>                  |                       | _                        | 1.5                | 2.0                      | ns    | 50% <sup>(2)</sup>                         |  |  |

| BEN Enable Time                                                 | t <sub>BEN</sub>      | _                        | 0.7                | 1.0                      | ns    | BEN 50% to CLK                             |  |  |

| CKO, SDO and CSO Logic High                                     | V <sub>OHO</sub>      | 1.95                     |                    |                          | V     |                                            |  |  |

| CKO, SDO and CSO Logic Low                                      | V <sub>OLO</sub>      | _                        | _                  | 0.35                     | V     |                                            |  |  |

- Note 1: Characterized only; not 100% tested in production.

- **2:** Design guidance only.

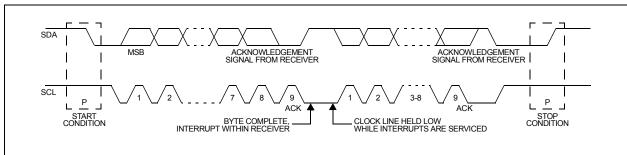

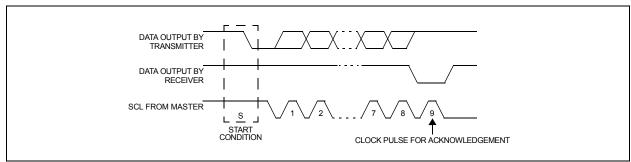

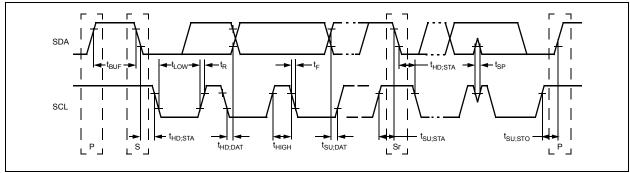

- **3:** A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to as the V<sub>IHmin</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- **4:** The maximum t<sub>HD,DAT</sub> only has to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- 5: A Fast mode  $I^2C$  bus device can be used in a Standard mode  $I^2C$  bus system, but the requirement of a  $t_{SU,DAT}$  of 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line,  $t_{Rmax} + t_{SU,DAT} = 1000 + 250 = 1250$  ns (according to the Standard mode  $I^2C$  bus specification), before the SCL line is released.

- **6:** The maximum t<sub>F</sub> for the SDA and SCL bus lines of 300 ns is longer than the specified maximum t<sub>of</sub> for the output stages, 250 ns. This allows series protection resistors (Rs) to be connected between the SDA/SCL pins and the SDA/SCL bus lines.

- 7: I/O pins of Fast mode devices must not obstruct the SDA and SCL lines if V<sub>LL</sub> is switched off.

## **HV7358**

#### TABLE 1-12: SPI AND I<sup>2</sup>C I/O CHARACTERISTICS (CONTINUED)

Unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V,  $V_{GN}$  = -5V,  $V_{SUB}$  = 0V, EN = 1,  $T_A$  = +25°C

| Parameters                                                                                                          | Sym.                | Min.                   | Тур. | Max.                  | Units | Conditions                              |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------|-----------------------|-------|-----------------------------------------|--|--|--|

| Fast I <sup>2</sup> C Interface I/O: SDA and SCL Pins                                                               |                     |                        |      |                       |       |                                         |  |  |  |

| Low-Level Input Voltage                                                                                             | $V_{IL}$            | -0.5                   | _    | 0.3 * V <sub>LL</sub> | V     |                                         |  |  |  |

| High-Level Input Voltage                                                                                            | V <sub>IH</sub>     | 0.7 * V <sub>LL</sub>  | _    | 0.5 + V <sub>LL</sub> | V     |                                         |  |  |  |

| Hysteresis of Schmitt Trigger Inputs <sup>(2)</sup>                                                                 | V <sub>hys</sub>    | 0.05 * V <sub>LL</sub> | _    | _                     | V     |                                         |  |  |  |

| Pulse Width of Spikes (which must be by the input filter suppressed) <sup>(1)</sup>                                 | t <sub>SP</sub>     | 0                      | _    | 50                    | ns    |                                         |  |  |  |

| Low-Level Output Voltage (open-drain or open-collector)                                                             | V <sub>OL6</sub>    | 0                      | _    | 0.6                   | V     | I <sub>SINK</sub> = 6 mA <sup>(1)</sup> |  |  |  |

| Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ with a bus capacitance of 10 pF to 400 pF, I = 6 mA <sup>(1)</sup> | t <sub>of6</sub>    | 20                     | _    | 250 <sup>(6)</sup>    | ns    |                                         |  |  |  |

| Input Current                                                                                                       | l <sub>i</sub>      | -10 <sup>(7)</sup>     | _    | 10 <sup>(7)</sup>     | μA    | 0.4V to 2.8V                            |  |  |  |

| I/O Capacitance <sup>(2)</sup>                                                                                      | Ci                  | _                      | _    | 10                    | pF    |                                         |  |  |  |

| SCL Clock Frequency                                                                                                 | f <sub>SCL</sub>    | _                      | _    | 400                   | kHz   |                                         |  |  |  |

| Bus Free Time, Stop to Start                                                                                        | t <sub>BUF</sub>    | 1.3                    | _    | _                     | μs    |                                         |  |  |  |

| Hold Time (Repeated) Start Condition                                                                                | t <sub>HD,STA</sub> | 0.6                    | _    | _                     | μs    | After this period, 1st                  |  |  |  |

| Low Period of the SCL Clock                                                                                         | $t_{LOW}$           | 1.3                    | _    | _                     | μs    |                                         |  |  |  |

| High Period of the SCL Clock                                                                                        | t <sub>HIGH</sub>   | 0.6                    | _    | _                     | μs    |                                         |  |  |  |

| Setup Time (Repeated) Start Condition                                                                               | t <sub>SU,SAT</sub> | 0.6                    | _    | _                     | μs    |                                         |  |  |  |

| Data Hold Time                                                                                                      | $t_{HD,DAT}$        | 0(3)                   | _    | 0.9 <sup>(4)</sup>    | μs    | Cbus compatible                         |  |  |  |

| Setup Time for Stop Condition                                                                                       | t <sub>SU,STO</sub> | 0.6                    | _    | _                     | μs    |                                         |  |  |  |

| Data Setup Time                                                                                                     | t <sub>SU,DAT</sub> | 100 <sup>(5)</sup>     | _    | _                     | ns    |                                         |  |  |  |

| Rise Time of SDA or SCL                                                                                             | t <sub>R</sub>      | 20                     | _    | 300                   | ns    |                                         |  |  |  |

| Fall Time of SDA or SCL                                                                                             | t <sub>F</sub>      | 20                     |      | 300                   | ns    |                                         |  |  |  |

| Capacitive Load for SDA or SCL                                                                                      | C <sub>b</sub>      | _                      | _    | 400                   | pF    |                                         |  |  |  |

- Note 1: Characterized only; not 100% tested in production.

- 2: Design guidance only.

- 3: A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to as the V<sub>IHmin</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- **4:** The maximum t<sub>HD,DAT</sub> only has to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- 5: A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement of a t<sub>SU,DAT</sub> of 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line, t<sub>Rmax</sub> + t<sub>SU,DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

- **6:** The maximum  $t_F$  for the SDA and SCL bus lines of 300 ns is longer than the specified maximum  $t_{of}$  for the output stages, 250 ns. This allows series protection resistors (Rs) to be connected between the SDA/SCL pins and the SDA/SCL bus lines.

- 7: I/O pins of Fast mode devices must not obstruct the SDA and SCL lines if  $V_{LL}$  is switched off.

TABLE 1-13: TX<sub>CH</sub> CLOCK AND PLL AC/DC CHARACTERISTICS

Over operating conditions unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{GN}$  = -5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V, EN = 1,  $T_A$  = +25°C

| Parameters                                           | Sym.              | Min. | Тур. | Max. | Units | Conditions                                                                                   |

|------------------------------------------------------|-------------------|------|------|------|-------|----------------------------------------------------------------------------------------------|

| V <sub>PLL</sub> Regulator Output Voltage            | V <sub>CPLL</sub> | 4.37 | 4.50 | 4.64 | V     | ±3%, T <sub>A</sub> = 5° to +75°C                                                            |

| PEN = 1 PLL Current Consumption                      | I <sub>VPLL</sub> | _    | 5.0  | 8.0  | mA    | V <sub>CPLL</sub> = 4.50V <sup>(2)</sup>                                                     |

| PEN = 0 PLL Current Consumption                      |                   | _    | _    | 3.0  | μA    |                                                                                              |

| Input Clock Frequency in Non-PLL mode                | f <sub>TCK</sub>  | 30   | _    | 200  | MHz   | PEN = LCKD = 0 <sup>(2)</sup>                                                                |

| Input Clock Frequency in PLL mode                    |                   | 30   | _    | 80   | MHz   | PEN = LCKD = 1 <sup>(2)</sup>                                                                |

| Clock Output Duty Cycle <sup>(2)</sup>               | D%                | 45   | 50   | 55   | %     |                                                                                              |

| VCO Frequency Range                                  | f <sub>VCO</sub>  | 160  | 240  | 250  | MHz   | At pin DNC1 <sup>(1)</sup>                                                                   |

| VCO Frequency Range Ratio (fmax/fmin) <sup>(2)</sup> | r <sub>fvco</sub> | _    | 1.56 | _    | _     |                                                                                              |

| Lock Time                                            | t <sub>LOCK</sub> | _    | 300  | 500  | μs    | f <sub>REF</sub> = 80 to 96 MHz jump <sup>(1)</sup>                                          |

| Bandwidth of PLL Loop                                | BW                | _    | 1.0  | _    | MHz   | In design now <sup>(2)</sup>                                                                 |

| f <sub>VCO</sub> Frequency Divider                   | N                 | 1    | _    | 8    | _     | Integer number: 1,2,3,4,5,6, 8 <sup>(1)</sup>                                                |

| Output f <sub>C</sub> Clock Integrated RMS Jitter    | t <sub>J</sub>    | _    | 15   | 20   | ps    | $f_{VCO} = 240 \text{ MHz},$<br>$f_{TCK} = 80 \text{ MHz}^{(2)}$                             |

| Output f <sub>C</sub> Clock Integrated RMS Jitter    | t <sub>JS</sub>   | _    | 15   | _    | ps    | $f_{VCO}$ = 240 MHz, $f_{TCK}$ = 80 MHz w/1%, 10 kHz V <sub>CPLL</sub> change <sup>(2)</sup> |

| Static Phase Error, 500 µs after LCKD = 1            | E <sub>PH</sub>   |      | ±50  | ±100 | ps    | $f_{VCO} = 240 \text{ MHz},$<br>$f_{TCK} = 80 \text{ MHz}^{(2)}$                             |

| Worst-Case Phase Jump Relock Time                    | t <sub>PJ</sub>   | _    | _    | 10   | μs    | $f_{VCO} = 240 \text{ MHz},$<br>$f_{TCK} = 80 \text{MHz}^{(2)}$                              |

**Note 1:** Characterized only; not 100% tested in production.

**2:** Design guidance only.

TABLE 1-14: TRSW AND RXDMP SWITCHES SWITCHING TIMING AND SPIKE VOLTAGES

Over operating conditions unless otherwise specified:  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  = +5V,  $V_{GN}$  = -5V,  $V_{PP}$  = +80V,  $V_{NN}$  = -80V, EN = 1,  $T_A$  = +25°C

| V <sub>NN</sub> 00 V, LIV - 1, I <sub>A</sub> - 123 O |                        |      |      |      |                  |                                                                           |

|-------------------------------------------------------|------------------------|------|------|------|------------------|---------------------------------------------------------------------------|

| Parameters                                            | Sym.                   | Min. | Тур. | Max. | Units            | Conditions                                                                |

| TRSW Switch-On Fixed Propagation Delay                | t <sub>TRSW</sub>      | _    | 200  |      | ns               | Addition to TRDLY<4:0> <sup>(1)</sup>                                     |

| TRSW Switch-On Programmable Delay                     |                        | 8    | _    | 288  | 1/f <sub>C</sub> | TRDLY<4:0> value <sup>(1)</sup>                                           |

| TRSW Switch-Off Delay Time                            |                        |      | 1.0  | 1.2  | μs               | TXRW fall to TRSW off, before TX <sub>CH</sub> next launch <sup>(1)</sup> |

| RTZSW Switch-On Delay Time                            | t <sub>RTZSW</sub>     | 8    | _    | 288  | 1/f <sub>C</sub> | TRDLY<4:0> I <sup>2</sup> C register value <sup>(1)</sup>                 |

| RTZSW Switch-Off Delay Time                           |                        | _    | 105  | _    | ns               | TXRW fall to RTZSW off <sup>(1)</sup>                                     |

| RXDMP Damp Switch-On Delay Time                       | t <sub>RXDMP</sub>     |      | 15.2 |      | ns               | TXRW fall to RXDMP on (1)                                                 |

| RXDMP Damp Switch-Off Delay Time                      |                        | l    | 1.1  |      | μs               | TRSW on to RXDMP off <sup>(1)</sup>                                       |

| TX <sub>CH</sub> Output Frequency Range in B mode     | f <sub>OUT</sub>       | 1    | 30   | 40   | MHz              | 100Ω resistor load <sup>(1)</sup>                                         |

| TRSW Turn-On Spike Voltage at TX <sub>CH</sub> Pins   | V <sub>TRSW_ON</sub>   |      | 80   | 110  | mVpk             | TX <sub>CH</sub> 50Ω load to GND <sup>(1)</sup>                           |

| TRSW Turn-Off Spike Voltage at TX <sub>CH</sub> Pins  | V <sub>TRSW_OFF</sub>  | -90  | -70  | _    |                  |                                                                           |

| RXDMP Turn-On Spike Voltage at RX <sub>CH</sub> Pins  | V <sub>RXDMP_ON</sub>  | _    | 45   | 60   |                  | RX <sub>CH</sub> 300 load to GND <sup>(1)</sup>                           |

| RXDMP Turn-Off Spike Voltage at RX <sub>CH</sub> Pins | V <sub>RXDMP_OFF</sub> | -70  | -60  |      |                  |                                                                           |

Note 1: Characterized only; not 100% tested in production.

**TABLE 1-15: TEMPERATURE SPECIFICATIONS**

| Parameters                              |                | Min. | Тур.  | Max. | Units | Conditions                                               |  |

|-----------------------------------------|----------------|------|-------|------|-------|----------------------------------------------------------|--|

| Temperature Ranges                      |                |      |       |      |       |                                                          |  |

| Operating Ambient Temperature Range     | T <sub>O</sub> | 0    | _     | +85  | °C    |                                                          |  |

| Storage Temperature Range               | T <sub>A</sub> | -55  | _     | +150 | °C    |                                                          |  |

| Junction Temperature                    | T <sub>J</sub> | _    | +125  | _    | °C    |                                                          |  |

| Package Thermal Resistances             |                |      |       |      |       |                                                          |  |

| Thermal Resistance Junction to Ambient  | $\theta_{JA}$  | _    | +16.5 | _    | °C/W  | JEDEC (2S2P) 4-Lead PCB,<br>114.3 mm x 76.2 mm x 1.6 mm, |  |

| Thermal Resistance Junction to PCB      | $\theta_{JB}$  | _    | +4.5  | _    | °C/W  | T <sub>A</sub> = +85°C                                   |  |

| Thermal Resistance Junction to Case Top | θЈС            | _    | +2.3  | _    | °C/W  |                                                          |  |

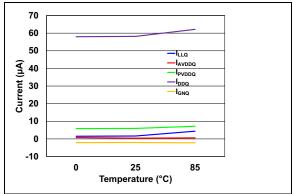

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:**  $V_{IN}$  = 12V,  $AV_{CC}$  =  $DV_{CC}$  = 5V,  $T_A$  = +25°C unless otherwise specified.

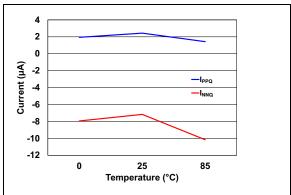

FIGURE 2-1: LV Supply Quiescent Current vs. Temperature (±70V, 5 MHz, 5 Cycles, PRF 2.5 kHz).

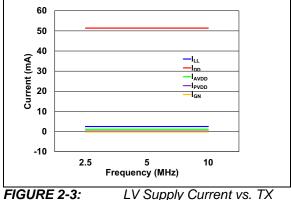

FIGURE 2-3: LV Supply Current vs. TX Frequency (±70V, 5 Cycles, PRF 2.5 kHz).

FIGURE 2-2: HV Supply Quiescent Current vs. Temperature (±70V, 5 MHz, 5 Cycles, PRF 2.5 kHz).

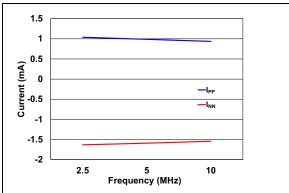

FIGURE 2-4: HV Supply Current vs. TX Frequency (±70V, 5 Cycles, PRF 2.5 kHz).

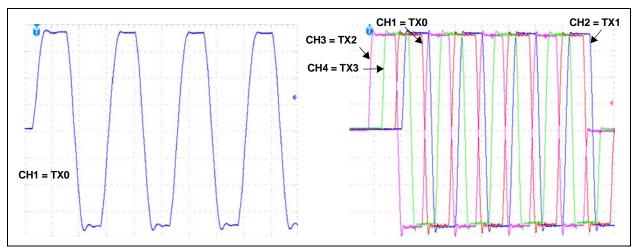

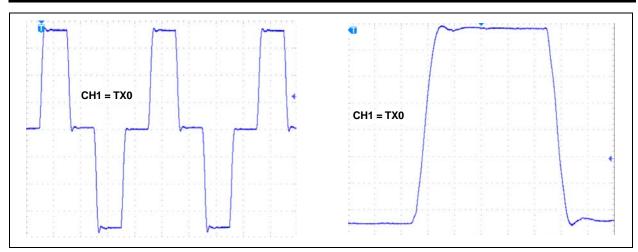

FIGURE 2-5: Typical Output Waveforms in B Mode Non-RTZ.

**Note:**  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  =  $PV_{DD}$  = +5V,  $V_{GN}$  = -5V,  $V_{PP}$  = +75V,  $V_{NN}$  = -75V. Load = 330 pF//2.5 kΩ, 5 MHz and 10 MHz Non-RTZ, BOC[1:0] = 00b, 200 ns delay between each channel.  $T_A$  = +25°C.

FIGURE 2-6: Typical Output Waveforms in B Mode RTZ.

**Note:**  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  =  $PV_{DD}$  = +5V,  $V_{GN}$  = -5V,  $V_{PP}$  = +75V,  $V_{NN}$  = -75V. Load = 330 pF//2.5 kΩ, 5 MHz RTZ with  $t_r/t_f$  measurements, BOC[1:0] = 00b.  $T_A$  = +25°C.

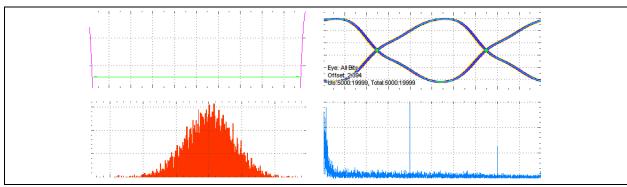

FIGURE 2-7: Typical B Mode Output Jitter with PLL Enabled.

**Note:**  $V_{LL}$  = +2.5V,  $AV_{DD}$  =  $V_{DD}$  =  $PV_{DD}$  = +5V,  $V_{GN}$  = -5V,  $V_{PP}$  = +15V,  $V_{NN}$  = -15V. Load = 330 pF//2.5 kΩ,  $f_{CLK}$  = 40 MHz, N = 100b,  $f_{C}$  = 200 MHz,  $f_{TX}$  = 5 MHz, PEN = 1, BOC[1:0] = 00b.  $T_{A}$  = +25°C.

### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION

| HV7358                                                                     | Symbol           | 1                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                            |                  | Description                                                                                                                                                                                                                                                                                                |

| C1, H1, L1, P1                                                             | V <sub>LL</sub>  | Logic Circuit Power Supply Pin: 0.22 μF ceramic cap to GND per pin.                                                                                                                                                                                                                                        |

| T4                                                                         | $AV_DD$          | Positive Power Supply Pin for Logic and PLL: +5V, 0.1 $\mu$ F + 1 $\mu$ F ceramic caps to GND per pin.                                                                                                                                                                                                     |

| C4, E3, H3,<br>L3, P4, P6                                                  | $V_{DD}$         | Positive Voltage Supply Input Pins: +5V, 1 μF ceramic cap to GND per pin.                                                                                                                                                                                                                                  |

| A7, B7, G8,<br>H8, R7, T7                                                  | $PV_{DD}$        | Positive Voltage Supply Input Pins for the RTZ N-Gate Drive: +5V, 1 $\mu F$ ceramic cap to GND per pin.                                                                                                                                                                                                    |

| A13, B13,<br>D15, H15,<br>M15, R13, T13                                    | V <sub>PP</sub>  | TX <sub>CH</sub> Positive Power Supply: +3V to +80V, 2 μF ceramic X7R cap to GND per pin.                                                                                                                                                                                                                  |

| A15, B15, F15,<br>K15, P15,<br>R15, T15                                    | V <sub>NN</sub>  | TX <sub>CH</sub> Negative Power Supply: -3V to -80V, 2 μF ceramic X7R cap to GND per pin.                                                                                                                                                                                                                  |

| A12, B12,<br>C15, G15,<br>L15, R12, T12                                    | CPF              | Internal $V_{PF}$ Gate Drive Voltage Linear Regulator Output Bypass Cap: 2 $\mu F$ 10V to $V_{PP}$ per pin.                                                                                                                                                                                                |